## Model Question Paper-1 with effect from 2019-20 (CBCS Scheme)

USN :

## Fourth Semester B.E. Degree Examination

## **Microcontroller and Embedded Systems**

# Time: 03 HrsMax. Marks:100

Note: Answer any FIVE full questions, choosing at least ONE question from each MODULE

#### Module-1

| 1. | a. Compare and Contrast microprocessor and microcontroller.                 | 4M |

|----|-----------------------------------------------------------------------------|----|

|    | b. Explain ARM core data flow model with a neat diagram.                    | 8M |

|    | c. Along with neat diagram of an ARM based embedded device (Microcontroller | ), |

|    | explain the four main hardware components.                                  | 8M |

#### OR

| 2. | a. Explain the different processor modes provided by ARM7.                   | 8M |

|----|------------------------------------------------------------------------------|----|

|    | b. Give the schematic of a Current Program Status Register of ARM7 processor |    |

|    | briefing the individual bits.                                                | 6M |

|    | c. What s Pipelining. Explain in detail schematically.                       | 6M |

#### Module-2

| 3. | a. Explain the MOV instruction set provided by ARM7 with the example for |    |

|----|--------------------------------------------------------------------------|----|

|    | each.                                                                    | 8M |

|    | b. Explain the ARM swap instruction with an example code.                | 6M |

|    | c. Brief about the categories of Load-Store instructions used with ARM.  | 6M |

#### OR

| 4. | a. Explain the ARM Single-Register and Multiple-Register load-store addressing |    |

|----|--------------------------------------------------------------------------------|----|

|    | modes with example.                                                            | 8M |

|    | b. Explain Co-Processor instructions of ARM Processor.                         | 6M |

|    | c. Write a note on Profiling and Cycle Counting.                               | 6M |

#### Module-3

| 5. | a. What are the different types of memories used in Embedded System design? |     |

|----|-----------------------------------------------------------------------------|-----|

|    | Explain the role of each.                                                   | 10M |

|    | b. List different purposes of embedded system with examples.                | 10M |

| 6. | a. Briefly Describe the classification of embedded systems | 8M  |

|----|------------------------------------------------------------|-----|

|    | b. Explain the following:                                  |     |

|    | i. I2C                                                     |     |

|    | ii.1-Wire Interface                                        |     |

|    | iii. SPI Interface                                         |     |

|    | iv. Reset Circuit                                          | 12M |

|    | Module-4                                                   |     |

| 7. | a. What are the operational and non-operational quality attributes of an embedd | ed  |

|----|---------------------------------------------------------------------------------|-----|

|    | systems.                                                                        | 10M |

|    | b. Explain the different types of serial interface bus used in Automotive       |     |

|    | Communication.                                                                  | 4M  |

|    |                                                                                 |     |

|    |                                                                                 |     |

c. Design FSM model for tea/coffee vending machine. 6M

# OR

| 8. a. Explain the fundamental issues in hardware software co-design.             | 6M      |

|----------------------------------------------------------------------------------|---------|

| b. Explain with a neat block diagram, how source file to object file translation | n takes |

| place.                                                                           | 8M      |

| c. Explain the different embedded firmware design approaches.                    | 6M      |

# Module-5

| 9. | a. With neat diagram explain operating system architecture.                        | 8M |

|----|------------------------------------------------------------------------------------|----|

|    | b. Differentiate between hard real time and soft real time operating system with a |    |

|    | example for each.                                                                  | 4M |

|    | c. Define process. Explain in detail the structure, memory organization and state  |    |

|    | transmission of the process.                                                       | 8M |

|    | OR                                                                                 |    |

| 10. | a. Explain the Simulator and Emulator.                  | 8M |

|-----|---------------------------------------------------------|----|

|     | b. Write a note on message passing.                     | 8M |

|     | c. Explain the concept of deadlock with a neat diagram. | 4M |

| Fourth-Semester B.E Degree Examination.                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mest 03 Hrs Micropolatroller & Embedded System.<br>Marks-100.<br>Subcokle = - 180544.                                                                                                                                                                                       |

| Module - 1.                                                                                                                                                                                                                                                                 |

| 1.a. compare 2 contrast microprocessor 2 microcontroller<br>- 4m.                                                                                                                                                                                                           |

| Microprocessor Microcontroller.                                                                                                                                                                                                                                             |

| <ol> <li>Most of the time, general<br/>purpose in design &amp; operation.</li> <li>Torgeted for high end<br/>movket where performance is<br/>important.</li> <li>Torinited power Saving options</li> <li>Timpared to micro controllegs</li> <li>Toring features.</li> </ol> |

| 4) It is a dependent unit, 4) It is a self-contained<br>unit.                                                                                                                                                                                                               |

| 9.6 Explain ARM core data frow mudel with a neaf<br>dragram? 8M.                                                                                                                                                                                                            |

| A programmer an think of an ARM core as<br>functional units connected by data buses, as shown<br>in the following fig.                                                                                                                                                      |

Data. Instruction decoder (rpi2 extend write Read. Register file Rd 1015 Result 80-715 A. RrofB RO B. LACC Barre) MAC Shifter ALV Address Register Thorementer Address.

Fig: ARM Care datations model. The arrows represent the Two of data, the lines represent the buses, and the boxes represent either on operation unit or a storage alea.

Data enters the Processor Core through the Data bus. The data may be instruction to execute Or a data item.

the instruction decoder translates instructions before they are executed toch instructions executed belonger to a particular instruction Set. the ARM Processor, like all ALSC Pricessors, Wes road-store architecture.

1. Load instructions copy clota from memory to registers in the Core.

2. Store instructions copy data trons registers to memory.

\* There are no data processing instructions that directly volaripulate data in memory, Thus data processing is careied out in registers.

- \* Data Herns are placed to the register file a storage bank made up of 32-bit registers.

- A ARM instructions typically have two Source register Rn I Rm I a singlest register rd.

- \* the ALV or MAC takes the register values Rn & Rm, from the A&B buses & computes aresult.

- A. After passing through the functional finits, the Besult in Rd is written back to the register file using the Result bus.

- A For load & Store instructions the incommenter updates the address register before the Core reads or writes the next register value form or to the Dext Sequential memory location.

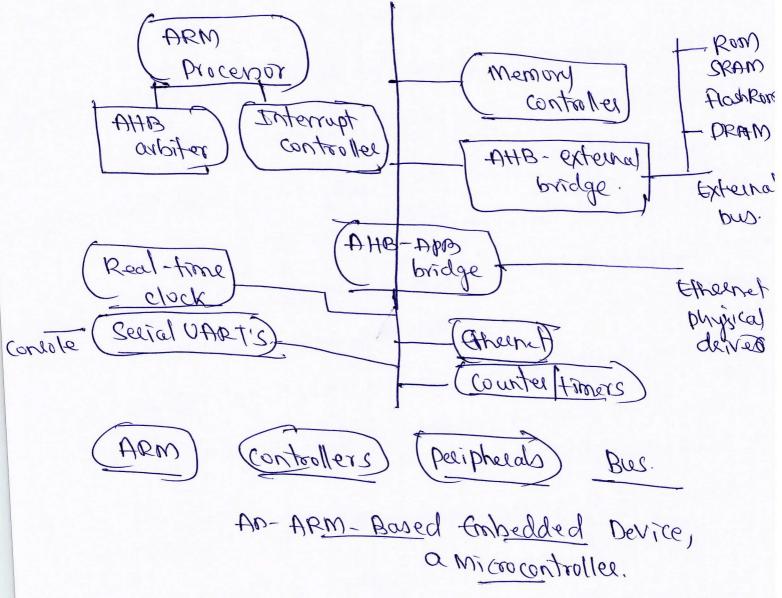

Le processor continues executing instructions C: Along with neat diagram of an ARM based embedded device (microcontextles) - Explain the four main hadwale components. Sm

the following figure shows a typical embedded device based on an ARM Core.

Each box represents a feature or tunction, the lines connecting the boxes are the buses careying data.

Ne can Seperate the device into tous main haidware components.

1. The ARM Procenor Controls the embedded device. 2. controllers co-ordinate important functional brucks of the System.

3. The periperals provide all the input-output copubility external to the Chip and are responsible for the uniqueness of the embedded device.

4 A bus is used to communicate between different posts of the device.

# OR.

2 a. Explain the different processor modes provided by ARM? 8m

the processor mode determines which registers are active & the access rights to the oper register itself. Each processor mode is either privileged or non-privileged.

1. A provilèged mode allows full read-write access to the oper.

2. A non-privileged mode only allows read accers to the control field in the CPSI, but still allows & read -write access to the condition flags. There are 7 processor modes in total. 1. SX privileged modes. 1. abort 3. fast interrupt request. 3. Interrupt request. 4. Supervisor 5. System 6. Undefined. 3. one non-privileged mode. 1. USer.

b. Give the schematic of a current proyon Statust egister of AKMA processor briefly the individual bits? Gro The ARM care uses the oper to monitor & control internal operations. the oper is a dedicated 32-bit register & register file. Fields tags Status Extension control. Bit 3 30 29 28 N Z C V I I F T Mode. Internet Thumb mode. Hags. State States State

Program Status register. The CPSY is divided into four fields, each 8 bit wide: flugs, Status, extension & control. The constrol field contains the

2) The flag field contains the condition flags.

c what is pipeling. Explain in detain schematically? A pipeline is the mechanism in a RISC Processor, which is used to execte instructions.

(Itern) Decode (Itxecute)

ARMI Three-Stage pipteline.

The above figure shows the three-stage pipeline.

- 1. fetch loads an instruction from memory.

- 2. Decede identifies the instruction to be executed.

3 Execute procenes the instruction & writes the result back to a register.

) Fetch Decode (Krewter Memory) Write)

ARMO Five-Stage pipeline.

Fetch #ssuet Decode Decode Memory Durite ARM 10 Six-Stage pipeline.

Module - 2. 3.a. Explain the MOV instructions set provided by ARMID with a Example for each? <u>800</u> Move instruction. Copies M into a destination registed Rd, where Mis aregister or a insta-ediate value. This instruction is useful for Setting Thirtid values 2 transferring data between registers. Syntax: Kinstruction> (Londs) Jsy Rd. N. MOV move a 32-bit value into a Rd=N. register

MNN move the Mot of the 32-bit Rd= ~rl. value into a register

PRE 85=5. 1) 87 = g. MOY 07, 15 Pust TS=S 67 = 5 MVN 05, 16.

11

> Aplain the ARM Swap instruction with an example code? En

The Swap instruction is a special case of a 10ad-Store instruction. It swaps the contents of memory with the contents of a register. Syntax: Ship (By (cond) & Rd. Rm, [Rn]

> trop = merosa[Rn] merosa[Rn] = Rm Rd = trop.

Stylp Swap a word between memory & a register

SWPB

Swap a byte between tmp=mem8[en] memory & a tegyster mem8[en]=Rm Rd=tmp.

r1 = 0×11112222

30. Brief about the categories of wad-Store instructions. used with ARM? En "Load-store instructions transfer data between memory & processor registers There are 3 types of load-Store instructions. () Single - register transfer. 2) multiple - register transfer. 3) Swap. 1) Single - Register transfor. These instructions are used for miving a Single data item in 2 out of a register. ' Syntax: <LDR[STR) & Kunds 3/By Rapiddrensing LDR L< cond) JSB [H] SI+ Rd, addressing. STR & Cond) & H Rd, addressing 2) multiple-register transfer. syntax : < LDM ISTM> ( Konds ) Koddrening mode Rudiy, Cregisters) d ~ y these instructions can transfer multiple registers between memory & the processor in a Strale Instruction

c) Swap Instruction. It swaps the contents of memory with the contents of a register. syntax: Sulpfield & Condely Rd, Rm, (Rn). tal Explain the PRIM Stryle-Register & Multiple-Register 12ad-store addressing modes with example? Em +. Single- register Franster. These instructions are used for moving a single data itemin & out of a register. & the datatypes supported are signed unsigned words, hafwords, bytes. Ex:- "LOR ro, [r]; = LOR ro, [r], #0] STR 80, [EI] ; = STR 80, [T1, #0] & multiple register transfer This can transfer multiple registers between memory 2 the processor in a single instruction. the transfer occurs from a base register En pointing with memory. multiple degister instructions are more efficien trom Single - Degister transfer for. 1. Miving blocks of data around memory. 9. Coving & roltoning context & stocke.

b. Explain &-processor instruction of Apr processor) for these are used to extend the instructions.

A co-processor can either provide additional computation capability or be used to control the memory subsystem including caches & memory management,

A co-processor instructions include data processing, register transfer, memory transfer instructions. Syntax: CDPL (cond) CP, Opladet, cd. En, diopladed) KmR demark & (cond) CP, opladet, Rd. G, CM, Opladed) KLDE (STC > d (cond)) CP, cd, addressing. CPP - co-processor data processing. MRC MCR - Co-processor register transfer. LDC STC Co-processor memory transfer.

Examble 2-MRC PIS, 0, 710, CO, 60, 0. 4.c. Write a note on profiling layde counting? 600 1- identify contral southers & maximeasure mul P their time. urhp2 histopedias privat plantapprication (10 1) Profilee: Tool to measure the cycle count consumed by any subroutine. and a cycle counting : Activity done by profileq. - - (1.0/7 5 stage Pipelining. 1. Fetch : collect operands) instruction. 2.10 pecide: understand instruction. 3- ALV .: Execute instruction. 4. LSI'S Load-store I updating result of Previous 5. LS2.; Load-Stored updating of previous Aluns1. in hard out justiced with a Instruction Address pc PC-4 pc-8 pc-12 pc-12. Action Fetch Perode Alv 191 182 (NETA W (972) TREASES STRATTER PARTY 200 is not preparent by the manifestances. in purpose of the surper sire to property

Sa what are the different types of memories used in Embedded System design? Explain the tole of each. Memories presentory is as insportant part of an processor (controller based Etabedded System. Program Storage memory (Rom) #+ can be classified into diff types as shown.

> PROM (ROM) PROM (ROM) PROM (ROM) (ROM) (ROM) EEPROM. EEPROM. ROM (MROM)

\* Masked-Rom: - It is a one-time programmable device.

It is the makes use of the hardwired technology for Storing data. I programmable kead only memory (OTP):-One-time programmable memory (OTP) or prom is not preprogrammed by the manufacturer. The end-when it records is a

these devices.

+ Epron (-crasable programmable Readonly memory):-It gives flexibility to se-program the same chip. It stores the bit information by Charging the floating gate of an FET: EEPROM ( Electrically frasable programmable Read 4 only memory), + The information contained in the EEPRom memory can be affered by using Electrical Signal at the register lbyte fevel, \* They can be crosed & regeageanmed in circuit. t Flash Flash memory is a Valiation of Eprom technolo flush memory is organized as seafors or pages. Non-Volatile RAM (NVRAM); k It is a random access memory with battle backap. the memory & bottery are packed in a single Package. The life Span of RIVRAM is expected to be

abound to years.

5b. List different purposes of embedded splein. with examples? 10m pata collection (storage Representation. Example: A Digital Conserve. 2. pata communication Example: - A wireless network douter. 3. Data (signal) Dorcessing. Examples - A digital bearing aid. 4. Monitoring Example: - Digital CRO. 5. (ontro) Examples - An Air Conditioner asystem. 6. Application Specific user interface. Example :- mobile phone. 6a. Briefly Describe the datsification of embedded some of the criteria used in the classification of embedded system are. Based on generation complexity & performance regts. 3. Based on deferministic behaviour. U. Randol on tregeletud.

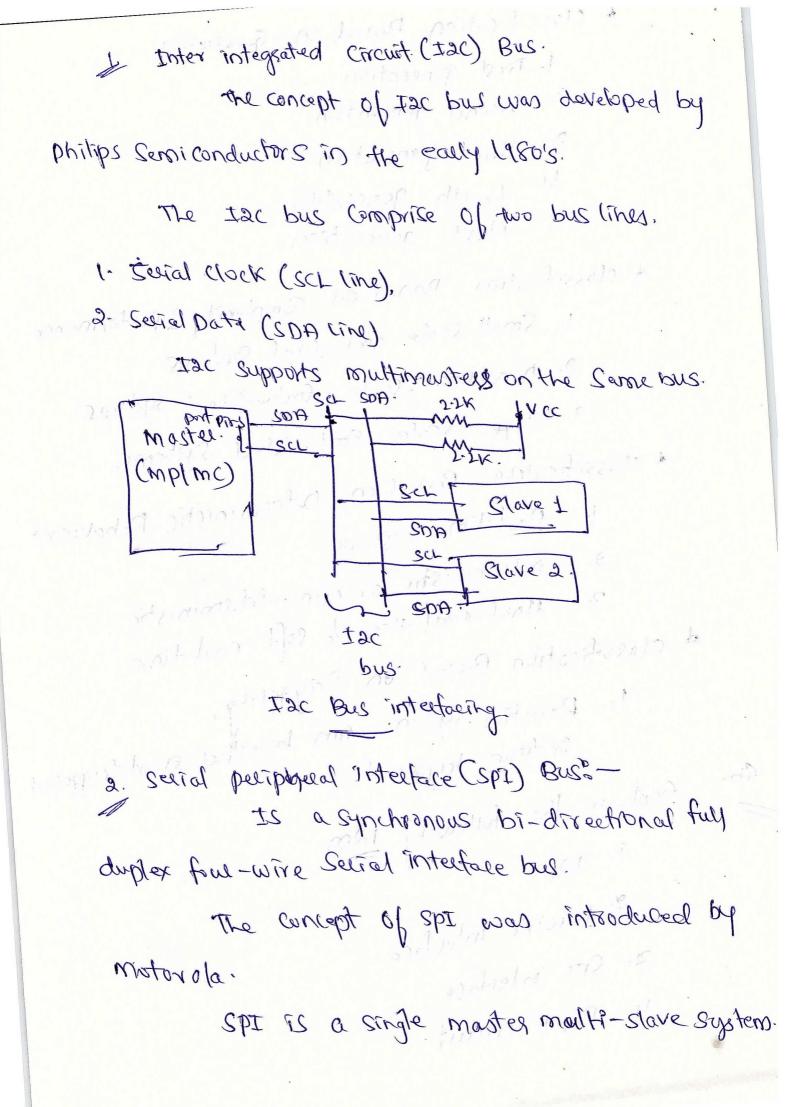

\* classification Based on Generation 1- First generation 2 Second generation 3. Third generation 4. Fourth Jenelation 5. Next generation. \* classification Based on Complexity & pectormance. 1. Small-Scale Embedded Systems 2- medium -scale trabedded systems. 3 large -Scale Embedded Systems. + classification Based on Deterministic Behavior: 1- Real time Systems. 2. Deterministic or non -deterministic. 3 Hard-real time & soft real time. A classification Based on Priggeling. 1. Reactive System can be either event triggered or time triggeled. 66. Explain the following 12m wit restruct 1. I2C. e) system ?! a' 1-voire interface. 3. SPI Interface. und que 4 - Reset arrant.

Spt requires fous Signal lines for communication 1. Most - master out slave in prin 2. MISO - Moster in Slave out. gua lity 3. SCLK - Secial Clock. T. SS. - Selection 5251-9629. 3. 1-wire Interface. It is also known as walles 1-wire protocol. Z4.7K. JGND Slavet. fig trog Mastel! (mp/mc) Do Stave 2 10/1 A GND.

1-wire Interface. Man 101241: -1 trey 1-wire device contains a globally anique 64-bit identification humber stored within it.

GND-

G.

Reset Circuit :-A reset is used at powel-on to hold th Processor in 'reset' until the power has stabilized. Dueing 'reset' the work is stopped, the registers & RAM are cleared & the program counter is set 10 Zero. Corrity out of reset, the clock is stal I the program Jumps to its starting address.

marines not real lampta such zonnijen Module -04. what are the operational knon-operational guality. ta attributes of an embedded systems? Lon Operational quality attributes. Response. Į. 8. Retrability 3 Security 189 4. Throughput-5. Maintainability. 6: Safety. Non-operational quality attributes. 1. Testability & Debug - ability.

2- Evolvabrility.

3. portability 4. Time to prototepe Amagkef. 5. per unit & total cost.

7.6. Explain the different types of secial interface bus used in Automotive commonication? Un 1. Controller Area Network (CAN). 2. Local Interconnect Network (CLINO)

3. The media = Oriented system transport (MOST). 1) CAN :-It is an event driver Secial protocol interface with Support for error handling in data transmission. 2) LINS it is a single master multiple slave Communication interface. 3. Most :- it is torgeted tor automotive audio vedro Equipment interfacing. 7C. Design FSM model for tea / coffee vending machine. Event: Tea Dispensed. Action: Done. Teu Button per State C. State insect win State B. A Déspense rea cancel Buttor Cottee Butterss Comout. (C1/12-5 Coffee Dispensed DISPANSe Coffee State D. FSM model. . wat isty Just and the with INTITUNE (right) and control is at some to add Witherexperies 102 Withere in the second II - switching UNAL 1970 34 012

8a. Explain the fundamental issues in hardwale. Saftwale co-design? Erg. 1- Selecting the model. 6- there models as used for copturing & describing the story chalacteristics & Selecting the Architechere. - A model only captures the system characteristics & does not provide information on how the system (on be manufactured? 3. The controller Architecture &- 14 maplements the finite state machine model using a state register & two combinational crecuits. a. The Dotapath Architecheres it is best suited for implementing the data-flow graph model where the obtput is generated as a result of a set of predefined computations on the ip data. 5. The finite state machine Deta path (FSMD) architecture :- It combines the controlleg architecture with data path Architecture. 6. The complex instruction Set computing (CISC) Architectule: - uses an instruction set representing complex operations. 7. The Reduced instruction Set computing (RISC) architectures - it reuses instruction set representing simple operations.

8. Selecting the language; A programming languager Captures a 'computation model' & maps it into architectule. e partitioning System Requirements into Hardware L'Software. 8.6. Explain with a neat block dragean, how Source file to object file translathon takes place? Sm se l'At Soulce file 1 library files ( osmor. src file) Module (module 1) Assemblel. Object file 1 Source file 2. Module (-asm or sec file) file a Accembtel. (to eluborn) Object to Her fild Absolute Convelter. object file Machine code (Hex file) Each source module is written in Assembly & is stored as orce file or asm file junt

On Successful accembla. 1 8.C. Explain the different embedded firmware design. approaches. 2 Em Two basic approaches all used for embedded firmwale design. 1. Conventional proceedural Based firmware design (Super loop model). 2- Embedded operating system (05) Based design. 1. Super loop model:-It is adopted for applications that are not time contral. It is very stroitar to a conventional Procedulal program ming where the code is executed task by task. the firmwale execution flow for this will be 1. configure the common palameters &. Stalt the first task & execute it. 3- Execute the Second task. 4. Execute the next task. C 6 ... 7- Execute the last defined task. timp back to the first task & follow the &.

2. The Embedded Operating System (25) Based approach. much care It contains operating systems, which can be either a (Gpos) or (RTOS) to host the wer written application fromwale. The General puppose OS (gpos) OS Based applications also require Drives 2. Softwale. The Real time operating System (REOS) 3. it allows flexible Schedulity of system retources. Module of all with half s. All fifting? cells anot boot it The with seat diagram explain operating system archifectule? 8m Application Application Azer programming <11 interface (API memory management (10 probas process Management Ringe Management Hurtpuss up to File system regent uni gortzota) 21121919 Ilo system mgmt IT. > Device dlivel?

Keenel :- it is the core of operating System. It is responsible for managing the strop resources & Communication arriving the Ww & Stw. 1. Meanvey regent. 2- process mgmt 170 3- Ame mgmt. u. file Stra mgmt. 5. Ilo sim mgmt. Differentrate between hard real time: I soft time operating system with a example for each? 4m Soft-Real time Sho. Hard Real Time Spr. ) It strictly adhere to the 17 doesn't qualantee () Meeting deadlines but tireity constraints for task is referred to as hard real offes best sfort to meet the deal deallin time slos. are referred as 8) This must meet the dealling Soft-real trove SIM for a task without any 3) Missing deallines Stippage tor tasks are acceptable 3. Missing deadlines leads to 3) It everphanis the princip if late answel is an Catastrophic results. acceptable answer

Define process Explains in detail the Structure, merenory organization & state transmission of the Vist2 plan process? 8m

A process is program or part of it in execution, it is also known as instance of program in-execution

No (seigx) ....) Process scientification 7. Stack (Stack pointer) 1 rt produced and on the shirt ions of off reduter Status regraters 2 a till u Program counter CPD 1. TRANSMAN (use memory Structure of a process corresponding to the process. publon memory organisation. of a process. M DIALL Stack memory · south Stack memory & grows downwards & grows wich and pouro proio. chiwowitz pitz Data memory of grows upwards Data memory

present in process are . The different states addemant reason 1. Created State. 21 plant a 2. Ready State and the zi li, allowing 3. Running State 4- Blocked State. 5- Completed State. Loa. Explain the Simulators & Enulator? Sin In circuit emulation (ICE) 15 the use of a hordware device or in-circuit remulator used to debug the software of an embedded system. An in-creat emulator also called on -circuit debugger (000) or Background debug Module (BDM) is a hardware device used to debug the SIW of an embedded System. ICE an also refer to the use of holdwale emulation, when the emulator is plugged into a syster in placeof aget-to-be built Chip. These in-circuit emulators provide away to run the System with "live" data while Still allowing

relatively good debugging Capabilities.

HISID VOT write a note on message passing? Em AT D) INTA message passing is an Calsynchronous information exchange prechanism wed for inter Process/Thread Communication. Based on message passing operation between processes, message passing is classified into 1) message queue. 2) Mail Box Signalling. Message gueare. Messeg quece Dert-zit Recieve Process 1 UNTON process à 2) Meuil box. Task pust meg 11:1111-14 Mailbox Broad Cast Broadcart Broadcart msg wez. 1.

3 Signalling :- it is primitive way for congraturic - tron . It is used for asynchronous notifications where one process thread is fires a signal, indicating occueance of a scenario which the other process threads in waiting. Explain the concept of deadlock with a 10.C Deat diagram? 400. Deadlock condition (reater a situation where none of the processor are able to make any pougeess in their execution, resulting in a set of deadlocked four conditions that must hold stimultaneously for these to be a deadlock. 1. Mutarial Execusion. 2. Hold & wait 3. Circulal waiting. 4- No-Preemption. top. PREPARED BY. (Sandeep P) Dean, Academics