## GBGS SCHEME

USN

18EC32

(08 Marks)

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Network Theory

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

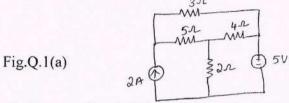

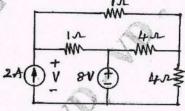

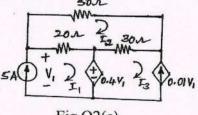

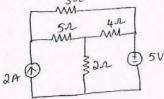

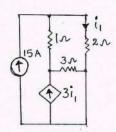

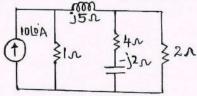

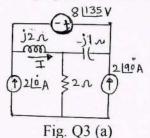

1 a. Using source transformation and source shifting techniques, find voltage across  $2\Omega$  resistor as shown in Fig.Q.1(a). (07 Marks)

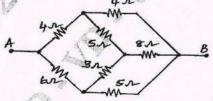

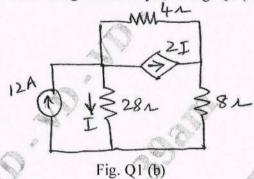

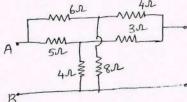

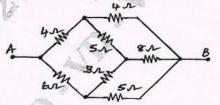

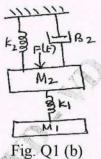

b. For the network shown in Fig.Q.1(b), find the equivalent resistance between A and B using Star-Delta transformation. (05 Marks)

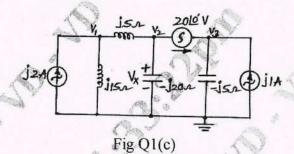

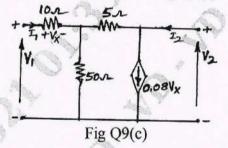

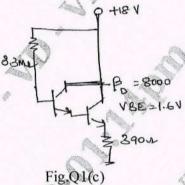

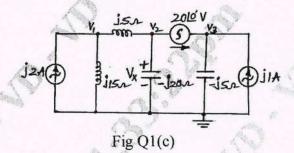

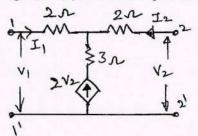

Determine the node voltages V<sub>1</sub> and V<sub>2</sub> by nodal analysis for the network in Fig.Q.1(c).

(08 Marks)

OR

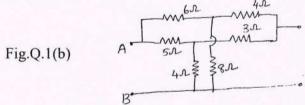

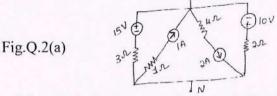

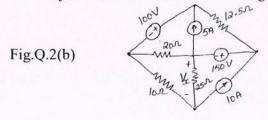

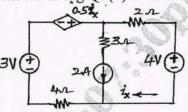

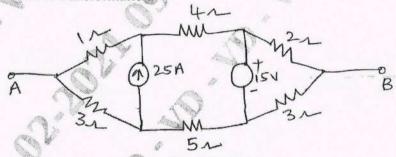

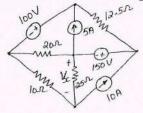

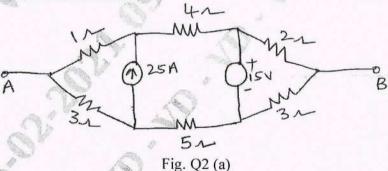

a. Find the potential difference between M and N using source transformation, for the network shown in Fig.Q.2(a).

(05 Marks)

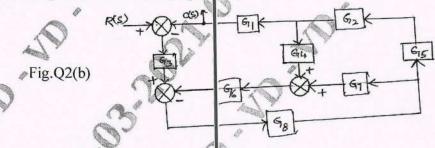

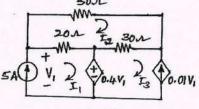

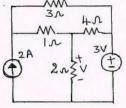

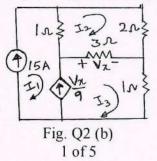

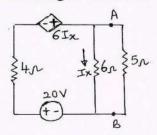

b. Find V<sub>x</sub> using nodal analysis for the network shown in Fig.Q.2(b).

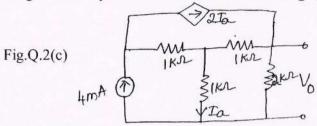

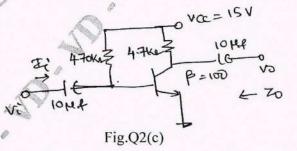

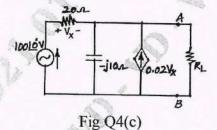

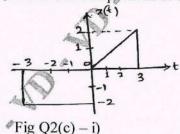

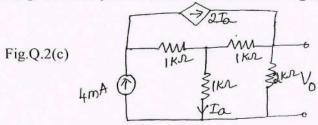

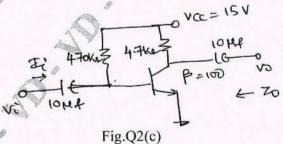

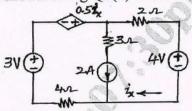

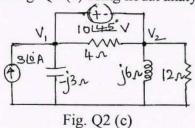

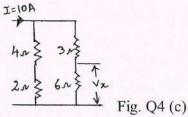

c. Determine V<sub>0</sub> using mesh analysis for the network shown in Fig.Q.2(c).

(07 Marks)

### Module-2

3 a. State and prove Millman's theorem.

(06 Marks)

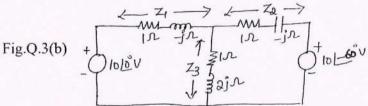

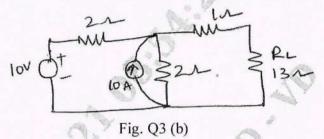

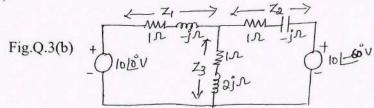

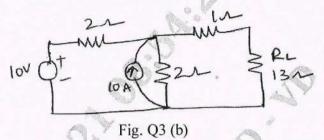

b. Find the current through Z<sub>3</sub> using superposition theorem for the network shown in Fig.Q.3(b). (10 Marks)

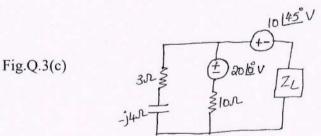

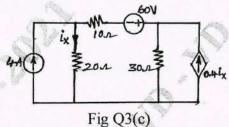

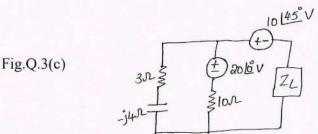

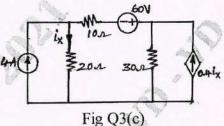

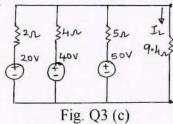

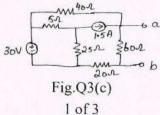

Find the value of Z<sub>L</sub> for which maximum power transfer occurs in the network shown in Fig.Q.3(c).

(04 Marks)

#### OR

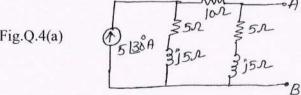

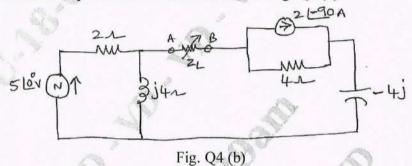

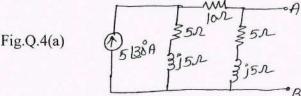

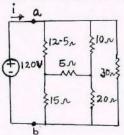

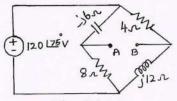

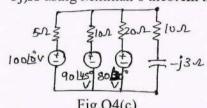

a. Obtain Thevenin's and Norton's equivalent circuit at terminals AB for the network shown in Fig.Q.4(a). Hence, find the current through 10Ω resistor across AB.

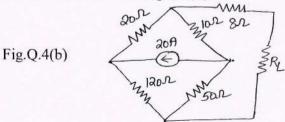

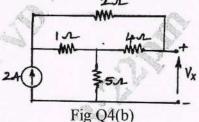

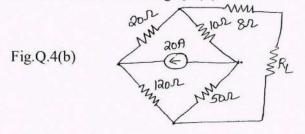

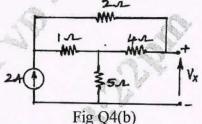

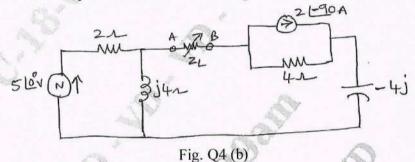

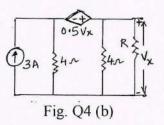

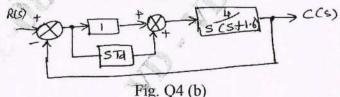

b. Find the value of R<sub>L</sub> for which maximum power is delivered. Also find the maximum power that is delivered to the load R<sub>L</sub>. Refer Fig.Q.4(b). (08 Marks)

2 of 4

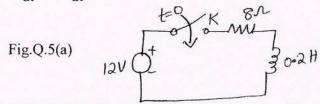

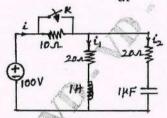

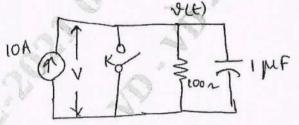

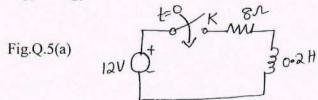

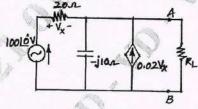

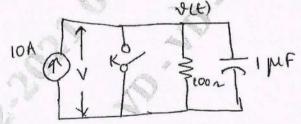

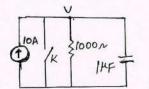

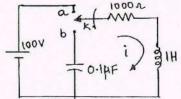

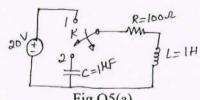

a. In the given network Fig.Q.5(a), K is closed at t=0, with zero current in the inductor. Find the values of i,  $\frac{di}{dt}$  and  $\frac{d^2i}{dt^2}$  at  $t = 0^+$ . (05 Marks)

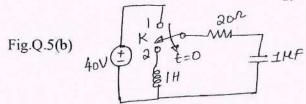

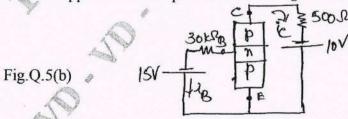

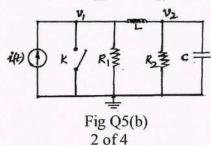

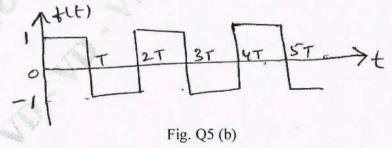

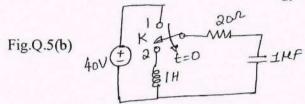

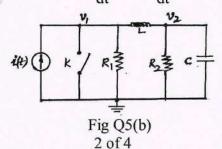

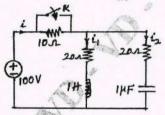

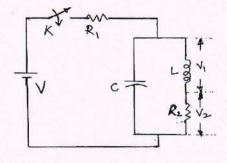

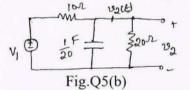

b. In the network Fig.Q.5(b), the switch is moved from position 1 to position 2 at t = 0. The steady-state has been reached before switching. Calculate i,  $\frac{di}{dt}$  and  $\frac{d^2i}{dt^2}$  at  $t = 0^+$ . (07 Marks)

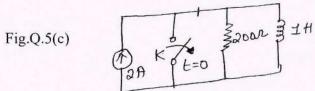

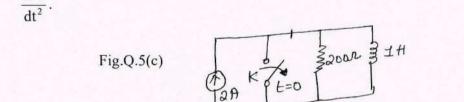

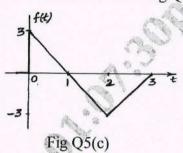

In the network Fig.Q.5(c), the switch K is opened at t = 0. At  $t = 0^+$ , solve for v,  $\frac{dv}{dt}$  and

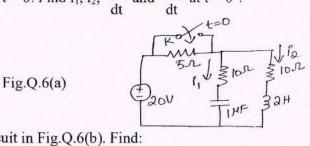

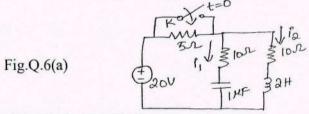

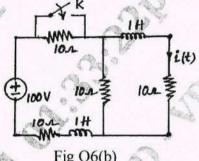

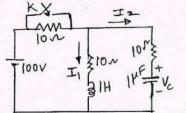

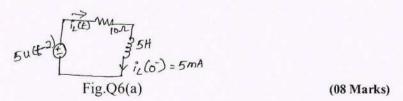

a. For the circuit shown in Fig.Q.6(a), steady state is reached with switch K open. The switch is closed at t = 0. Find  $i_1$ ,  $i_2$ ,  $\frac{di_1}{dt}$  and  $\frac{di_2}{dt}$  at  $t = 0^+$ . (10 Marks)

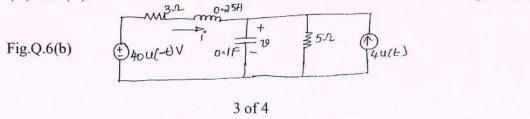

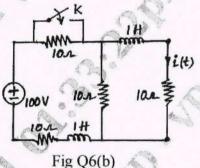

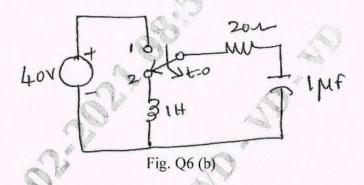

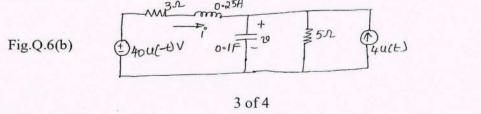

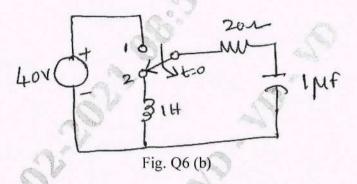

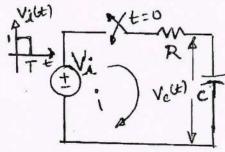

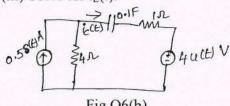

- b. For the circuit in Fig.Q.6(b). Find:

- i)  $v(0^{+})$  and  $i(0^{+})$

- $\frac{dv(0^+)}{dt}$  and  $\frac{di(0^+)}{dt}$

- $v(\infty)$  and  $i(\infty)$ . iii) (10 Marks)

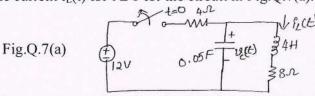

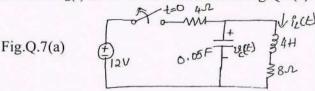

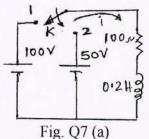

7 a. Determine the current  $i_L(t)$  for  $t \ge 0$  for the circuit in Fig.Q.7(a).

(10 Marks)

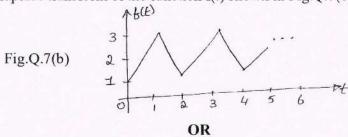

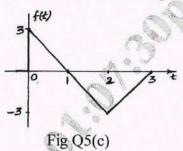

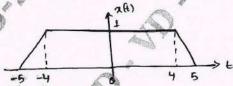

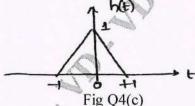

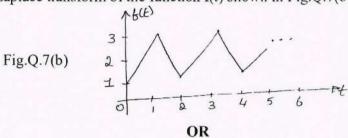

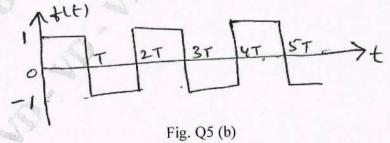

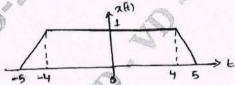

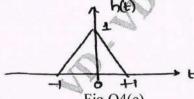

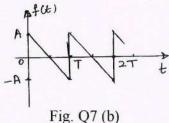

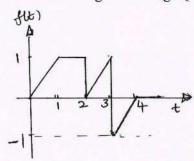

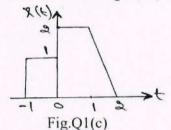

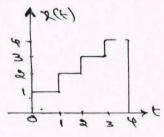

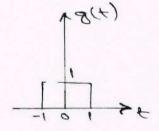

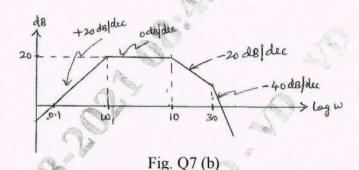

b. Find the Laplace transform of the function f(t) shown in Fig.Q.7(b).

(10 Marks)

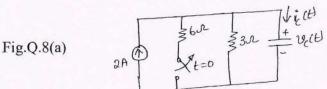

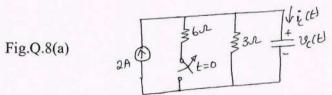

8 a. Determine the voltage v<sub>c</sub>(t) and the current i<sub>c</sub>(t) for t ≥ 0 for the circuit shown in Fig.Q.8(a).

(10 Marks)

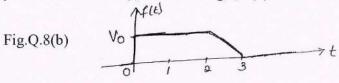

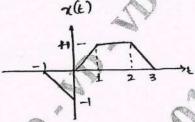

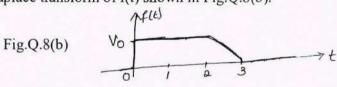

b. Find the Laplace transform of f(t) shown in Fig.Q.8(b).

(10 Marks)

Module-5

9 a. Express Y parameters in terms of h-parameters.

(06 Marks)

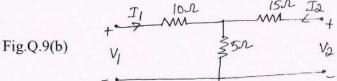

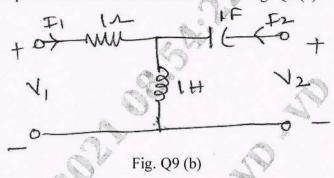

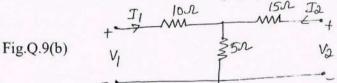

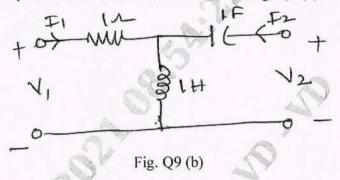

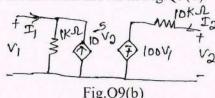

b. Find Z-parameters for the network shown in Fig.Q.9(b).

(06 Marks)

c. The Z-parameters of a two port network are  $z_{11} = 20\Omega$ ,  $z_{22} = 30\Omega$ ,  $z_{12} = z_{21} = 10\Omega$ . Find Y and ABCD parameters of the network. (08 Marks)

OR

- 10 a. Prove that the resonant frequency is the geometric mean of the two half power frequencies.

(06 Marks)

- b. A series RLC circuit has  $R = 10\Omega$ , L = 0.01H and  $C = 0.01\mu F$  and it is connected across 10mv supply. Calculate: i)  $f_0$  ii)  $Q_0$  iii) bandwidth iv)  $f_1$  and  $f_2$  v)  $I_0$ . (06 Marks)

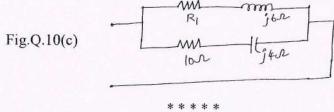

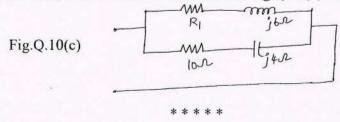

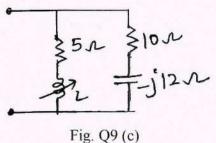

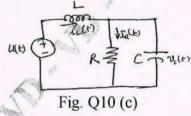

- c. Find the value of R<sub>1</sub> such that the circuit shown in Fig.Q.10(c) is resonant. (08 Marks)

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Electronic Devices

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- a. Write the figures of the resulting orbitals when isolated atoms brought together and explain the characteristics. (10 Marks)

- Obtain the relationship between mobility and hall coefficient in a p-type bar placed in a magnetic field in the Z-direction.

OR

- a. Derive the equation which relates current density and mobility in a semiconductor in an applied electric field.

(10 Marks)

- b. A silicon bar 2μm long and 200μm² in cross sectional area is doped with 1.5 × 10<sup>17</sup>/cm³ phosphorus. Find the current at 300K with 30V applied voltage. How long does it take an average electron to drift 2μm in pure silicon at an electric field of 80V/cm? Also calculate the time required at 10<sup>5</sup>V/cm. Assume mobility of electrons is 0.1350m²/Vsec. Also assume that saturation of electron drift velocity for silicon is 10<sup>7</sup> cm/s for the electric field above 10<sup>5</sup> V/cm.

Module-2

- 3 a. Show the effect of bias at a pn junction on transition region width, electric field, electrostatic potential, energy band diagram partic flow and current direction under the following conditions:

- i) Equilibrium

Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice.

- ii) Forward bias

- iii) Reverse bias.

(10 Marks)

b. Illustrate the care and issues to be considered in the design of solar cells.

(10 Marks)

OR

4 a. Explain Avalanche break down and obtain equation for the electron multiplication factor.

(10 Marks)

b. Derive the relationship between the open circuit voltage and optic generation rate starting from the expression for the optically generated illuminated pn junction. (10 Marks)

Module-3

- 5 a. Show the hole and electron flow in a pnp transistor with proper biasing. (08 Marks)

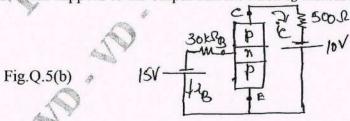

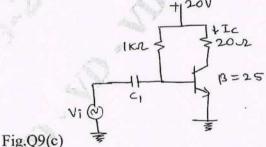

- b. For the circuit shown in Fig.Q.5(b) calculate  $\beta$ ,  $I_B$  and  $I_C$ . Given that  $\tau_p = 18\mu s$ , and  $\tau_t = 0.2\mu s$ . What happens to the output current when  $I_B$  increases and  $\beta$  increases?

(06 Marks)

c. Explain the concept of base narrowing in a  $p^+ - n - p^+$  transistor. 1 of 2

(06 Marks)

\$

#### OR

- 6 a. Obtain the Ebers-Moll equations and represent the same in the model form. (12 Marks)

- b. Describe the switching effects in a CE transistor circuit.

(08 Marks)

#### Module-4

- 7 a. Analyze the effect on gate-to-channel-space charge region and IV characteristics for the following conditions in a JFET:

- i) Zero gate voltage of a small drain voltage

- ii) Zero gate voltage of a large drain voltage

- iii) Small V<sub>DS</sub> value and small reverse-biased gate voltage.

(10 Marks)

- b. Draw the energy band diagram in an MOS capacitor structure for the following cases:

- i) p-type substrate for a positive gate bias

- ii) p-type substrate for a large positive gate bias

- iii) n-type substrate for a positive gate bias.

(10 Marks)

#### OR

- 8 a. Write the small signal equivalent circuit of a JFET, ideal low frequency small signal equivalent circuit and ideal equivalent circuit including r<sub>s</sub>. (10 Marks)

- b. Show the channel formation in the MOS structure and I<sub>D</sub> versus V<sub>DS</sub> curve for the following cases:

- i)  $V_{gs} > V_t$  and small  $V_{DS}$  value

- ii)  $V_{gs} > V_t$  and large  $V_{DS}$  value

- iii)  $V_{gs} > V_t$  and  $V_{DS} = V_{DS}$  (sat)

(10 Marks)

#### Module-5

- 9 a. What are the fabrication steps used in the fabrication of pn junctions? (10 Marks)

- b. With figures, describe the complementary MOS structure.

(10 Marks)

#### OR

10 a. Illustrate the evolution of integrated circuits.

(10 Marks)

b. Explain the formation of resistors in integrated circuits

(10 Marks)

## CBCS SCHEME

| USN |  |  |  |  | 18EC34 |

|-----|--|--|--|--|--------|

|-----|--|--|--|--|--------|

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Digital System Design

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing one full question from each module.

Module-1

- a. Design a logic circuit that has 4 inputs, the output will be high, when the majority of the inputs are high. Use K-map to simplify.

(07 Marks)

- b. Express the following functions into canonical form:

(i)  $f_1 = ab' + ab' + bc$

(ii)  $f_2 = (a + b')(b' + c)$

(06 Marks)

- c. Identify all the prime implicants and essential prime implicants of the following using K-map.

- i)  $f(a, b, c, d) = \sum m(6, 7, 9, 10, 13) + dc(1, 4, 5, 11, 15)$

- ii)  $f(a, b, c, d) = \pi M(1, 2, 3, 4, 9, 10) + dc(0, 14, 15)$

- iii)  $F(w, x, y, z) = \Sigma(0, 2, 4, 5, 6, 7, 8, 10, 13, 15)$

(07 Marks)

OR

2 a. Simplify the following using tabulation methods:

$Y = \Sigma m(1, 2, 3, 5, 9, 12, 14, 15) + \Sigma d(4, 8, 11)$

(07 Marks)

- b. Simplify the following expression using K-map. Implement the simplified expression using NAND gates only.  $F = \Sigma m(0, 1, 2, 5, 6, 7, 8, 9, 10, 13, 14, 15)$ . (07 Marks)

- c. Explain briefly K-map, incompletely specified functions, essential prime implicants and gray codes. (06 Marks)

Module-2

a. Design a two bit magnitude comparator.

(10 Marks)

(05 Marks)

b. Realize the following functions expressed in maxterm canonical form in two possible ways using 3:8 decodes.  $f_1(a, b, c) = \pi M(1, 2, 6, 7)$  and  $f_2(a, b, c) = \pi M(1, 3, 6, 7)$  (10 Marks)

OR

- 4 a. Implement  $f(a, b, c, d) = \sum m(0, 1, 5, 6, 7, 9, 10, 15)$ , using;

- (i) 8:1 mux with a, b, c, as select lines (ii) 4:1 mux with a, b as select lines. (08 Marks)

- b. Explain 4-bit carry look-ahead adder with necessary diagram and relevant expressions.

(04 Marks)

- c. Draw a PLA circuit to implement the logic function A'BC + AB'C + AC' and A'B'C' + BC.

(08 Marks)

Module-3

- 5 a. Explain with timing diagrams the workings of SR latch as a switch debouncer. (08 Marks)

- b. What is race around condition? Explain JK Master Slave flipflop with a diagram, function table and timing diagram. (07 Marks)

- c. List the difference between combinational and sequential circuits.

#### OR

- 6 a. Explain the operation of clocked SR flipflop using NAND gates. (07 Marks)

- b. What is the significance of Edge Triggering? Explain the working of positive edge triggered

D-FF with their function table. (07 Marks)

- c. Explain the working of 4-bit twisted ring counter using necessary diagram and logic table.

(06 Marks)

### Module-4

- 7 a. Using positive edge triggering SR flipflops design a counter which counts in the following sequence: 000, 111, 110, 101, 100, 011, 010, 001, 000 ... (10 Marks)

- b. Design a synchronous mod-6 counter using D-flipflop to generate the sequence (0, 2, 3, 6, 5, 1, 0) (10 Marks)

#### OR

8 a. Write the difference between Mealy and Moore model with necessary diagrams. (10 Marks)

b. Explain state machine notations with an example. (10 Marks)

### Module-5

- Construct Mealy state diagram that will detect input sequence 10110, when input pattern is detected, Z is asserted high. Give state diagram for each state.

(10 Marks)

- b. With necessary diagram, explain the concept of serial adder with accumulators. (10 Marks)

#### OR

- 10 a. Design a sequential circuit to convert BCD to excess 3 code. (10 Marks)

- Explain the design of sequential circuit using CPLD's and give CPLD implementation of a shift register and parallel adder with accumulator. (10 Marks)

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Power Electronics and Instrumentation

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- 1 a. Discuss various power converter circuits with necessary sketches and applications of each.

(07 Marks)

- b. With necessary sketches, explain the static V-I characteristics of SCR and its operation.

(08 Marks)

- c. List different turn-on methods, explain all in brief.

(05 Marks)

OR

- 2 a. Explain turn-ON/turn-OFF dynamic characteristics of SCR with neat diagram. (07 Marks)

- b. With suitable diagram and waveform, explain the working of RC full wave firing circuit.

(08 Marks)

c. Describe the operation of UJT with neat sketches.

(05 Marks)

### Module-2

- a. Explain the working of 1φ full wave center tapped controlled rectifier for resistive load with necessary sketches and also develop mathematical model to evaluate performance parameter of same (V<sub>dc</sub>, V<sub>rms</sub>, Efficiency).

- b. Evaluate performance parameter of  $1\phi$  half controlled rectifier with resistive load, has a transformer secondary voltage of 230V, 50Hz with  $R=10\Omega$  and firing angle  $\alpha=60^\circ$ . Determine:

- i) Average voltage and current

- ii) Rms value of voltage and current

- iii) Efficiency

- iv) Ripple factor

- v) Form factor.

(10 Marks)

OR

- 4 a. Input to the step-up chopper is 200V the output required is 600V, if the conduction time of thyristor is 200μsec. Compute:

- i) Chopping frequency

- ii) If the pulse width is halved for constant frequency operation, find the new output voltage. (07 Marks)

- Explain the operation step-up chopper with neat diagram and derive an expression for output voltage.

- Elaborate on the control techniques used in choppers and also give detailed classification of choppers.

(05 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

- a. With neat circuit diagram and waveforms. Explain the operation of 1φ full bridge inverter for RL load.

(07 Marks)

- b. Design a multi range ammeter with range 0-1A, 0-5A and 0-10A employing individual shunt in each a D'Arsonval movement with an internal resistance of 500Ω and full scale deflection of 10mA is available.

- c. What are the errors encountered in measurement process? Explain all with suitable example.

(05 Marks)

#### OR

6 a. Design modified multirange voltmeter with basic D'Arsonval movement with an internal resistance of 50Ω and full scale deflection of 2mA, with voltage ranges of 0-10V, 0-50V, 0-100V and 0-250V. Draw the schematic diagram and show all values after design.

(07 Marks)

b. Explain the various static characteristics of measuring instruments.

(08 Marks)

c. With neat diagram, explain the operation of isolated flyback converter.

(05 Marks)

### Module-4

7 a. With neat block diagram, explain the operation of Ramp type Digital voltmeter. (07 Marks)

b. Explain the operation of Time measurement with neat block diagram.

(08 Marks)

c. Draw the schematic diagram of Wheatstone's bridge and derive an expression for calculating unknown resistance and explain. (05 Marks)

#### OR

- 8 a. Explain the operation inductance comparision bridge with necessary equations. (07 Marks)

- b. Discuss the operation of successive approximation type DVM with necessary diagram.

(08 Marks)

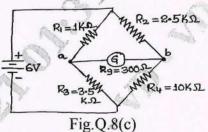

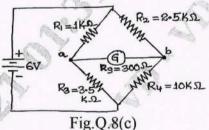

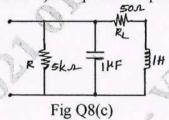

c. An unbalanced Wheatstone bridge shown in Fig.Q.8(c), calculate the current through the galvanometer. (05 Marks)

#### Module-5

- 9 a. Draw the schematic diagram to measure displacement using resistive transducer and explain.

(07 Marks)

- b. Explain the operation of PLC with neat block diagram. (05 Marks)

- c. Explain the operation of Instrumentation amplifier using transducer bridge and derive equation for output voltage. (08 Marks)

#### OR

10 a. Explain the construction and working principle of LVDT with characteristic curve.

(07 Marks)

b. What are factors to be considered for selecting the transducer?

(08 Marks)

c. Illustrate working of analog weight scale.

(05 Marks)

\* \* \* \* \*

## GBGS SCHEME

|     |  | <br> | <br> |    |           |        |

|-----|--|------|------|----|-----------|--------|

| USN |  |      |      | li | Carlot A. | 17EC33 |

|     |  |      |      |    |           |        |

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Analog Electronics

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- a. What is BJT transistor modeling? Obtain the expression for voltage gain, Z<sub>in</sub> and Z<sub>o</sub> of CB configuration using AC equivalent circuit with re model. (05 Marks)

- b. Derive the expression for A<sub>i</sub>, A<sub>v</sub>, Z<sub>i</sub> and Z<sub>o</sub> for a voltage divider bias circuit of BJT, with unbypassed RE, using re equivalent model of BJT. Show the phase relationship between input and output wave form.

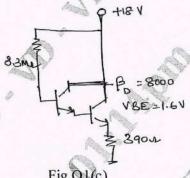

- c. State the characteristic features of Darlington connection. Calculate the DC bias voltages and currents in the circuit.

(05 Marks)

#### OR

- 2 a. Give the relation between re parameters and h parameters. What are the advantages of h parameters? (05 Marks)

- b. Derive the expressions for current gain, voltage gain, input impedance and output impedance for an emitter follower circuit using approximate hybrid equivalent circuit. (Without the effect of r<sub>o</sub>).

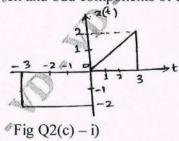

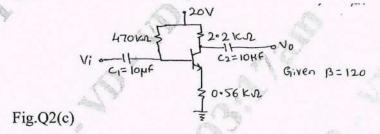

- c. For the network shown in Fig.Q2(c), determine re,  $Z_i$ ,  $Z_o$ ,  $A_v$  (with  $r_o = \infty \Omega$ ) and  $A_v$  (with  $r_o = 50 \text{ KO}$ )

(05 Marks)

#### Module-2

- 3 a. Explain the construction of N channel JFET. Also explain the drain and transfer characteristics of the JFET. (06 Marks)

- b. With equivalent circuit obtain the expression for Z<sub>o</sub> and A<sub>v</sub> for JFET self bias configuration.

(08 Marks)

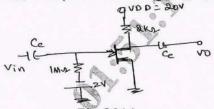

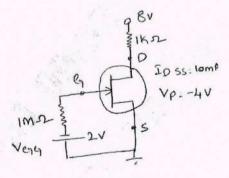

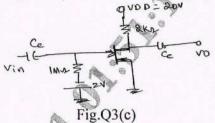

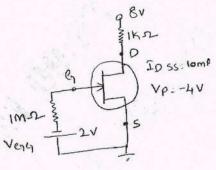

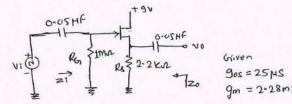

c. The fixed bias configuration shown in Fig.Q3(c) has  $V_{GSQ} = -2V$ ,  $I_{DQ} = 5.625$  mA with  $I_{DSS} = 10$  mA,  $V_P = -8V$  and  $Y_{OS} = 40$   $\mu$ S. Determine  $g_m$ ,  $r_d$ ,  $Z_o$  and  $A_v$ .

(06 Marks)

(10 Marks)

OR

- 4 a. Differentiate between enhancement and depletion MOSFET. (05 Marks)

- b. With necessary equivalent circuit, obtain the expression for A<sub>v</sub> for a JFET source follower configuration.

(05 Marks)

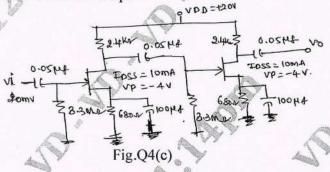

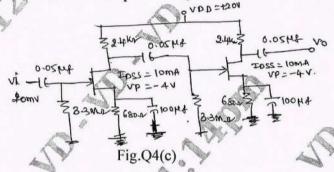

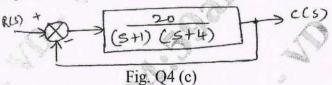

- c. Calculate the DC bias, voltage gain, input impedance and output impedance and resulting output voltage for the cascade amplifier shown in Fig.Q4(c). Calculate the load voltage if a  $10 \text{ K}\Omega$  load is connected across the output.

Module-3

5 a. Determine the lower cutoff frequency flox for the voltage divider bias network using the following parameters:

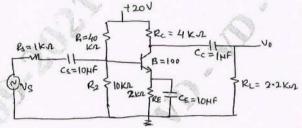

$C_S = 10 \ \mu f, \ C_E = 20 \ \mu f, \ C_C = 1 \ \mu f, \ R_S = 1 \ K\Omega, \ R_1 = 40 \ K\Omega, \ R_2 = 10 \ K\Omega, \ R_E = 2 \ K\Omega, \ R_C = 4 \ K\Omega, \ R_L = 2.2 \ K\Omega, \ \beta = 100, \ r_o = \infty\Omega, \ V_{CC} = 20 \ V, \ re = 15.76 \ \Omega.$  (04 Marks)

- b. Explain the following: (i) Logarithm (ii) Decibel. With respect to transistor amplifier calculate the overall lower 3 dB and upper 3 dB frequencies for a 3 stage amplifier having an individual  $f_1 = 40$  Hz and  $f_2 = 2$  MHz. (06 Marks)

- c. Discuss the low frequency response of BJT amplifier and give expression for lower cut off frequency due to C<sub>C</sub>, C<sub>E</sub> and C<sub>S</sub>.

(10 Marks)

ÓR

- a. Draw the Hybrid π model for the transistor in CE configuration and explain the significance of each component.

(06 Marks)

- b. Describe the Miller effect and derive an equation for Miller input capacitance. (06 Marks)

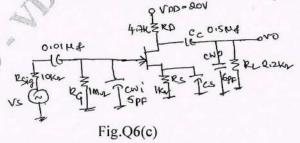

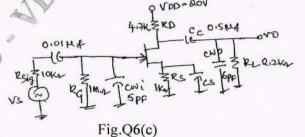

- c. Determine the high cutoff frequencies for the network shown in Fig.Q6(c).

(08 Marks)

- 7 a. With a block diagram, explain the concept of feedback amplifier and derive the expression for  $A_f = \frac{A}{1 + A\beta}$ . (06 Marks)

- b. Derive the expression for Z<sub>if</sub> and Z<sub>of</sub> for current series feedback amplifier. (08 Marks)

- c. Explain a practical voltage series feedback circuit.

(06 Marks)

OR

- 8 a. What is an oscillator? Discuss the concept of generating oscillations with the help of Barkhausen criteria. (05 Marks)

- b. With a neat circuit diagram and necessary expressions, explain the Wein bridge oscillator.

(10 Marks)

- c. Design a unijuction transistor for a operation at 1 kHz and 150 kHz assuming  $\eta = 0.58$ .

(05 Marks)

Module-5

- 9 a. Give the definition of power amplifiers and list the types of power amplifiers based on the location of Opoint. (05 Marks)

- b. Explain the working of class B complementary symmetry class B push pull amplifier.

Obtain an expression for maximum conversion efficiency of this amplifier. (10 Marks)

- c. Calculate the harmonic distortion components for an output signal having fundamental amplitude of 2.5 V, second harmonic amplitude of 0.25 V, third harmonic amplitude of 0.1 V and fourth harmonic amplitude of 0.05 V and also calculate the total harmonic distortion for the amplitude components given above.

(05 Marks)

OR A

- 10 a. With necessary circuit diagram and characteristic curve, explain the class-A transformer coupled amplifier. Show that the maximum efficiency can be expressed as 50%. (10 Marks)

- b. Describe the block diagram of series and shunt type voltage regulators. (05 Marks)

- c. Calculate the output voltage and Zener current un the regulator circuit of Fig.Q10(c) for

Vi \$=50

Vo (regulated)

(curregulated) \$220,4

1 VZ

12:V

Fig.Q10(c)

(05 Marks)

| USN |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|

17EC34

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Digital Electronics

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- 1 a. Define the following:

- i) Combinational circuit

- ii) Sequential circuit

- iii) Canonical SOP

- iv) Canonical POS

- v) Prime Implicant

- vi) Essential prime implicant.

(08 Marks)

- b. Express the following equations into decimal notations:

- i) H = f(A, B, C) = A'BC + A'BC + ABC

- ii) T = f(a, b, c) = (a + b' + c) (a + b' + c') (a' + b' + c)

(08 Marks)

c. Write mirror image version 5-variable K-map.

(04 Marks)

OR

- 2 a. Obtain minimal expression using k-map for the following incompletely specified function  $F(a, b, c, d) = \sum m(0, 1, 4, 6, 7, 9, 15) + \sum d(3, 5, 11, 13)$  and draw circuit diagram using gates. (10 Marks)

- b. Simplify the following using Quine-Mcclusky method  $s = f(w, x, y, z) = \sum (1, 3, 13, 15) + \sum d(8, 9, 10, 11)$

(10 Marks)

Module-2

- 3 a. Explain the analysis and design procedure for combinational circuit with example. (10 Marks)

- b. Implement full substractor using 3:8 decoder and write truth table.

(10 Marks)

OP

4 a. Design full adder using i) 8:1 MUX ii) 4:1 MUX.

(10 Marks)

b. Design 4 to 16 decoder using 3 to 8 decoder.

(05 Marks)

Explain look ahead carry adder and give its advantages and disadvantages.

(05 Marks)

Module-3

- 5 a. What is flipflop? Discuss working principle of SR flipflop with its TT and write characteristics equations. (10 Marks)

- b. Sketch timing diagram for JK flipflop and D-flipflop.

(05 Marks)

c. Explain the operation of a switch debouncer built using SR-latch with the help of waveforms. (05 Marks)

#### OR

- 6 a. Explain the working of a master-slave JK flip-flop with timing diagram. Show how race around condition is eliminated. (10 Marks)

- b. Explain setup time, hold time and propagation delay for timing considerations. (05 Marks)

- c. Write characteristics equation for D and T flip-flop.

(05 Marks)

#### Module-4

- a. Explain with diagram, operation and waveforms Serial In Serial Out (SISO) shift left mode register.

(10 Marks)

- b. Design BCD ripple counter using JK flip-flop.

(10 Marks)

#### OR

8 a. Design an synchronous mod 5 counter using JK flip-flop and draw its timing diagram.

(10 Marks)

b. Explain ring counter with timing sequence.

(05 Marks)

c. Write a note on Johnson counter.

(05 Marks)

#### Module-5

- 9 a. Draw and explain the block diagram of Moore and Mealy model with example and also compare both. (10 Marks)

- b. Define, present state, next state, state diagram state table and state assignment. (05 Marks)

- c. Draw and explain Moore JK-flipflop state diagram.

(05 Marks)

#### OR

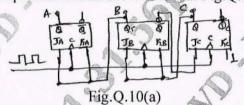

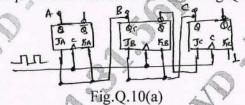

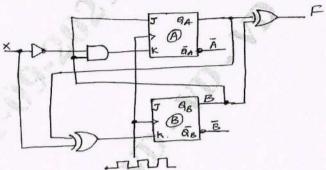

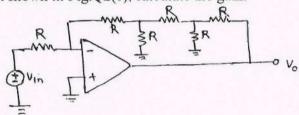

10 a. Analyze the synchronous sequential circuit show below in Fig.Q.10(a).

(12 Marks)

b. Design a synchronous counter using JK flipflops to count the sequence 0, 1, 2, 4, 5, 6, 0, 1, 2. Use state diagram and state table. (08 Marks)

\* \* \* \* \*

# Third Semester B.E. Degree Examination, Jan./Feb. 2021 Network Analysis

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- 1 a. Define controlled source and mention its types. Also, mention its applications. (05 Marks)

- b. Using source shift and source transformations, determine the voltage across the current source in Fig Q1(b).

Fig Q1(b)

(05 Marks)

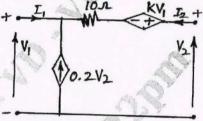

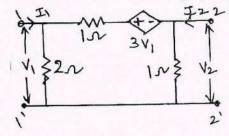

c. For the circuit of Fig Q1(c), use nodal analysis to determine the voltage labeled V<sub>x</sub>

(10 Marks)

OR

2 a. Define and explain supermesh.

- (04 Marks)

- b. Use Star-Delta transformations to find the equivalent resistance at AB in Fig Q2(b).

Fig Q2(b)

(06 Marks)

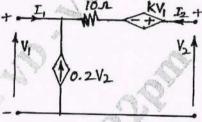

c. Use Mesh analysis to determine V<sub>1</sub> and the power being supplied by the dependent current source in the circuit shown in Fig Q2(c).

Fig Q2(c)

(10 Marks)

3 a. State and explain Millman's theorem for AC circuit.

(05 Marks)

b. Use superposition on the circuit shown in Fig Q3(b) to find the current ix.

Fig Q3(b)

(05 Marks)

c. Use Norton's theorem for the circuit of Fig Q3(c) to determine the power absorbed by the  $20\Omega$  resistor.

(10 Marks)

OR

- 4 a. State and prove maximum power transfer theorem for AC voltage source with internal impedance connected to variable impedance. (06 Marks)

- b. Verify reciprocity theorem for the circuit of Fig Q4(b).

(04 Marks)

c. For the circuit of Fig Q4(c), what value of R<sub>L</sub> will absorb a maximum average power, and what is the value of this power?

(10 Marks)

Module-3

- 5 a. Explain the behavior of R, L and C elements for transients. Mention their representation at  $t = 0^+$  (06 Marks)

- b. In the network of the Fig Q5(b), is in the steady state with the switch K closed. At t = 0, the switch is opened. Find the values of  $v_1$ ,  $v_2$ ,  $\frac{dv_1}{dt}$  and  $\frac{dv_2}{dt}$  at  $t = 0^+$ .

(08 Marks)

c. Find the Laplace transform of the waveform shown in Fig Q5(c)

(06 Marks)

OR

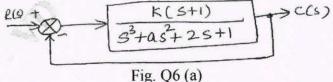

a. In the network of the Fig Q6(a), a steady state is reached with the switch K open. AT time t = 0, the switch is closed. Find the values of  $i_1$ ,  $i_2$ ,  $\frac{di_1}{dt}$  and  $\frac{di_2}{dt}$  at  $t = 0^+$ .

Fig Q6(a)

(10 Marks)

b. In the network of the Fig Q6(b), the switch K is closed at t = 0 a steady state having previously excited. Draw the transform network and find the current i(t), using the Laplace transformation method.

(10 Marks)

Module-4

7 a. In a series resonant circuit, show that resonant frequency is equal to the geometric mean of half-power frequencies. (06 Marks)

An R-L-C series circuit of 8Ω resistance should be designed to have a bandwidth of 50Hz.

Determine the values of L and C, so that the system resonates at 250Hz. Also determine the half power frequencies.

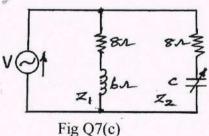

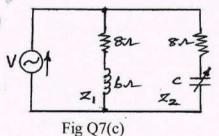

c. For the network shown in Fig Q7(c), determine the value of C at which it resonates when f = 100Hz. Also find the values of  $R_L$  and  $R_C$  at which the circuit resonates at all frequencies.

(08 Marks)

- 8 a. Define the following terms pertaining to a series R-L-C circuit, i) Resonance ii) Quality factor iii) Bandwidth iv) Selectivity. (04 Marks)

- b. A series R-L-C circuit with an input voltage  $5 | \underline{0}^{\circ} V|$  resonates at a frequency of 8400Hz. The peak value of current is 500mA at resonance and the bandwidth is 120Hz. Determine the values of R, L, C and cut-off frequencies. (06 Marks)

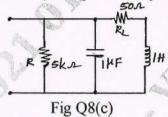

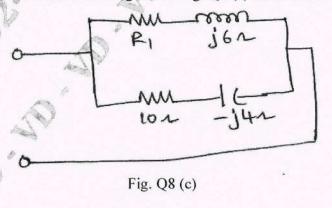

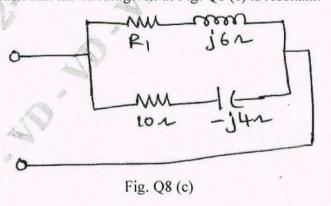

- c. For the network shown in Fig Q8(c), determine; i) Resonance frequency ii) Input admittance iii) Quality factor iv) Bandwidth and v) half power frequencies.

(10 Marks)

### Module-5

9 a. Obtain Y-parameters in terms of z-parameters.

(06 Marks)

b. Find hybrid parameters for the two part shown in Fig Q9(b). What value of K in the two-part of figure shown will produce reciprocal network.

Fig Q9(b)

(06 Marks)

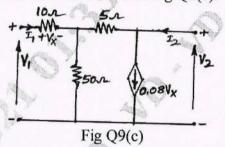

c. Determine the ABCD parameters for the network of Fig Q9(c)

(08 Marks)

#### OR

- 10 a. Explain h-parameters with equivalent circuit. Also obtain t-parameters in terms of h-parameters and hence show that AD BC = 1. (10 Marks)

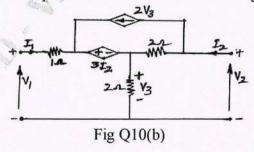

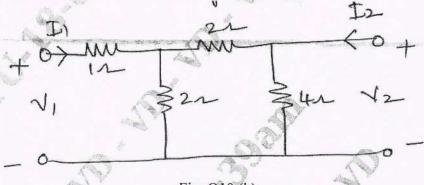

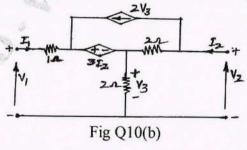

- b. Find the Z-parameters and the Y-parameters for the network of Fig Q10(b)

(10 Marks)

\*\*\*\*\*

4 of 4

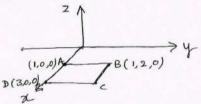

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Engineering Electromagnetics

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

1 a. State and explain Coulomb's Law in vector form.

(04 Marks)

b. Derive the expression for electric field intensity due to infinite line charge.

(08 Marks)

c. Let a point charge  $Q_1 = 25$ nc be located at A(4, -2, 7) and a charge  $Q_2 = 60$ nc be at B(-3, 4, -2). Find  $\vec{E}$  at C(1, 2, 3). Also find the direction of the electric field. Given  $\epsilon_0 = 8.854 \times 10^{-12}$  F/M.

#### OR

- a. Define electric field intensity and flux density also derive an expression for electric field intensity E at a point due to many charges.

- b. Point charges of 50nc each are located at A(1, 0, 0), B(-1, 0, 0), C(0, 1, 0) and D(0, -1, 0)m find the total force on the charge at A and also find E at A. (08 Marks)

- c. A uniform line charge of infinite length with  $P_L = 40$ nc/m, lies along the Z-axis. Find  $\vec{E}$  at (-2, 2, 8) in air. (05 Marks)

#### Module-2

3 a. State and prove Gauss Law for point charge.

(06 Marks)

b. Define potential difference and absolute potential.

(04 Marks)

c. In the given relation  $D = 4xy \hat{a}_x + 2(x^2 + y^2) \hat{a}_y + 4yz \hat{a}_z c/m^2$ . Evaluate both sides of the divergence theorem and find the charge enclosed within the rectangular parallelpiped  $(0 \le x \le 2)$ ,  $(0 \le y \le 3)$  and  $(0 \le z \le 5)m$ .

#### OR

4 a. State and prove divergence theorem.

(04 Marks)

b. Derive point form of continuity equation for current.

(08 Marks)

- c. A point charge of 6nc is located at origin in free space, find potential of point P, if P is located at (0.2, -0.4, 0.4) and

- i) V = 0 at infinity

- ii) V = 0 at (1, 0, 0)

- iii) V = 20V at (-0.5, 1, -1).

(08 Marks)

### Module-3

5 a. State and prove uniqueness theorem.

(08 Marks)

By applying Laplace equation find the expression for capacitance between the two concentric spheres. Make suitable assumptions. (12 Marks)

OR

6 a. Derive the expressions for Poisson's and Laplace's equation.

(04 Marks)

b. State and explain Biot – Savart Law.

(06 Marks)

- c. Given the potential field  $V = [Ar^4 + Br^{-4}]\sin 4\phi$ :

- i) Show that  $\nabla^2 V = 0$

- ii) Find A and B such that V = 10V and  $\vec{E} = 500V/m$  at  $P(r = 1, \phi = 22.5^{\circ}, z = 2)$ . (10 Marks)

### Module-4

- 7 a. Derive an expression for magnetic forces on :

- i) Moving point charge and

- ii) Differential current element.

(10 Marks)

b. Two differential current elements,

$$I_1 \Delta \stackrel{\rightarrow}{L_1} = 10^{-5} \, \hat{a}_2 \text{ A.M at P}_1(1, 0, 0) \text{ and}$$

$$I_2 \Delta \vec{L}_2 = 10^{-5} (0.6 \hat{a}_x - 2 \hat{a}_y + 3 \hat{a}_2) \text{A.M at P}_2(-1, 0, 0)$$

are located in free space. Find vector force exerted on  $I_2 \Delta \vec{L}_2 = I_1 \Delta \vec{L}_1$ . (10 Marks)

#### OR

- Drive the magnetic boundary conditions at the interface between the two different magnetic materials. Discuss the conditions.

(10 Marks)

- b. A sq. loop carrying 2mA current is placed in the field of an infinite filament carrying current of 15Amp as shown in Fig.Q8(b). Find the force exerted on the sq loop.

Fig.Q8(b).

(10 Marks)

#### Module-5

9 a. Write a Maxwell's equations in point form and integral form.

(06 Marks)

- A uniform plane wave with an intensity of electric field equal to 1volt/m is travelling in free space. Find the magnitude of the associated magnetic field. (04 Marks)

- c. State and explain pointing theorem.

(10 Marks

#### OR

10 a. State and explain Faraday's Law of electromagnetic induction. (0

(04 Marks)

- Starting from Maxwell's equation obtain the general wave equations in electric magnetic fields.

(08 Marks)

- c. A UPW with 10MHz frequency has average pointing vector  $1W/m^2$  if the medium is perfect dielectric with  $\mu_r = 2$ , and  $\epsilon_r = 3$ ,  $\mu_0 = 4\pi \times 10^{-7} H/m$ ,  $\epsilon_0 = 8.854 \times 10^{-12} F/m$ ; Find:

- i) Velocity

- ii) Wavelength

- iii) Intrinsic impedance

- iv) rms value of electric field.

(08 Marks)

\* \* \* \* \*

### 17EC45

(04 Marks)

## Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 Linear Integrated Circuits

Time: 3 hrs. Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

#### Module-1

- 1 a. Define the following terms with respect to op-amp and mention their typical values

(i) CMRR (ii) PSRR (iii) Slew Rate (iv) I/P Offset voltages (v) Input bias current

(10 Marks)

- b. Sketch the circuit of an op-amp difference amplifier. Discuss the working common mode nulling capability with necessary circuit modifications and equations. (10 Marks)

#### OR

- 2 a. With a neat circuit diagram, explain the basic operational amplifier circuit. (06 Marks)

- b. A non-inverting amplifier is to amplify a 100 mV signal to a level 5V. Using 741 op-amp design a suitable circuit. Also calculate the input and output impedances. (08 Marks)

- c. With a neat circuit diagram, explain inverting summing amplifier and derive for output voltage and show how it can be converted into averaging circuit. (06 Marks)

#### Module-2

- a. Sketch the circuit of a High Z<sub>in</sub> capacitor Coupled Non-inverting amplifier and explain its working with necessary design steps. Show that the input impedance is very high compared to capacitor coupled Non-Inverting amplifier. (10 Marks)

- b. Design a capacitor coupled Inverting amplifier using op-amp 741 to have a voltage gain of 50 and an output voltage of 2.5 V. The input signal frequency ranges from 10 Hz to 1 kHz with a load resistance of 250 Ω.

- c. What are the advantages of precision rectifiers over ordinary rectifiers?

#### OR

- 4 a. Draw the circuit of an instrumentation amplifier and explain. Also show the method of nulling common mode outputs and how dc output voltage can be level shifted and list the features of instrumentation amplifier. (10 Marks)

- b. With a neat sketch, explain the working of a precision voltage source with zener diode and op-amp.

(05 Marks)

- Explain how upper cutoff frequency can be set in Non-Inverting and Inverting capacitor coupled circuits.

#### Module-3

- 5 a. Draw and explain an op-amp sample and hold circuit with necessary waveforms. (08 Marks)

- Explain the working of Weinbridge oscillator using op-amp with a neat sketch of circuit, waveforms and equations. Design the same to get output frequency of 15 kHz with +/- 12 power supply using IC 741.

- c. With a neat circuit diagram, explain a multiplier using op-amp. (04 Marks)

(04 Marks)

#### OR

- a. With a neat sketch, explain Inverting Schmitt trigger circuit with necessary waveforms and equations. Also design the same using IC741 op-amp to have UTP = 0V and LTP = 2V with +/- 12V power supply.

- Sketch the circuit of fundamental log amplifier. Explain its working and derive for output voltage. What is the drawback of fundamental log amplifier and how it can be eliminated in temperature compensated log amplifier. (10 Marks)

#### Module-4

- 7 a. Sketch the circuit of second order active high pass filter using bipolor op-amp and explain its working. Design the same for a cutoff frequency of 7 kHz. (08 Marks)

- Show how a bandpass filter can be constructed by the use of lowpass and high pass filters.

Draw the circuit of a single stage band pass filter and explain the operation with necessary design equations.

- List the advantages of active filters over passive filters.

#### 2

- 8 a. With a neat diagram, explain the operation of IC 723 as high voltage regulator. Design the same to have  $V_0 = 12V$  and  $I_0 = 2A$ . (08 Marks)

- Discuss the performance parameters of a three terminal IC regulator can be used as a current source.

- c. List the important characteristics of a three terminal IC regulator. (04 Marks)

#### Module-5

- With a neat circuit diagram, explain the working of IC 566 voltage controlled oscillator with necessary waveforms. Also derive for output frequency.

(08 Marks)

- b. With a neat circuit diagram and waveforms explain the working of R-2R network D-A converter and derive the expression for output voltage. (08 Marks)

- c. What is the output voltage produced by a DAC with output range of 0V to 10V for the given binary input number is (i) 0110 (for 4 bit DAC) (ii) 10111011 (for 8 bit DAC). (04 Marks)

#### OR

- 10 a. Draw the internal schematic of IC 555, configure it for a stable operation and explain with necessary equations and waveforms.

(10 Marks)

- b. Explain the working of successive approximation Analog to Digital Converter (ADC).

(10 Marks)

\* \* \* \* \*

## CBCS SCHEME

| USN |  |  |  | H |  |

|-----|--|--|--|---|--|

|-----|--|--|--|---|--|

17EC46

## Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 Microprocessors

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- 1 a. Draw and explain the internal architecture of 8086 microprocessor. (10 Marks)

- b. Explain the concept of segmented memory. What are its advantages? (06 Marks)

- c. If (CS) = 2000H, (DS) = 1234H, (SS) = 5678H, (BP) = 09ABH, calculate the physical address generated by the microprocessor when the following instruction is executed: MOV AL, [BP + 55H].

#### OR

- a. With one example for each, describe any five addressing modes of 8086, used to access the data present in memory.

(10 Marks)

- b. List out any six conditional branch instruction that work based on the condition of any one flag. Mention the flag corresponding to each instruction. (06 Marks)

- c. With numerical examples, illustrate the use of CBW and CWD instructions. (04 Marks)

### Module-2

- 3 a. List out the five string manipulation instructions of 8086 and explain the operation of each.

(10 Marks)

- b. Write an Assembly Language Program (ALP) to add the data word located at address 2000H: 0500H to another data word available at offset 0600H in the same segment, and store the result and carry starting at 0700H in the same segment. (06 Marks)

- With numerical examples, bring out the difference between SAR and SHR instructions.

(04 Marks)

#### OR

- 4 a. Write an ALP using assembler directives to convert a 4-digit packed BCD number into equivalent 16-bit binary number, and store the result in memory. Write comments in your program.

(10 Marks)

- b. Explain the following instructions with one example each: RCR, XOR, SAHF. (06 Marks)

- c. State the difference between the following two instructions: AND, TEST. What is the use of these instructions? (04 Marks)

#### Module-3

- 5 a. Explain the structure of stack in 8086 microprocessor. What is the role of stack during CALL and RET instructions? Illustrate with example. (10 Marks)

- b. Explain any three methods of passing the parameters to and from a procedure. (06 Marks)

- c. What is a macro? Give any two differences between macro and procedure. (04 Marks)

#### OR

- 6 a. Draw the interrupt vector table of 8086 and explain how an interrupt request is serviced, taking the example of type N interrupt. (10 Marks)

- b. Write an ALP to generate a time delay of 10 seconds using an 8086 system that runs on 10MHz frequency. (06 Marks)

- c. Bring out any four differences between maskable and non-maskable interrupts. (04 Marks)

#### Module-4

- 7 a. With a neat diagram, explain the maximum mode 8086 system. (10 Marks)

- b. Write the functions of the following signals of 8086: i) ALE ii)  $\overline{\text{DEN}}$  iii)  $\overline{\text{BHE}}$ .

(06 Marks)

c. Draw the minimum mode read cycle timing diagram, and explain briefly.

(04 Marks)

#### OR

- 8 a. Design an interface between 8086 and two ICs of 32KB RAM and two ICs of 16KB EPROM. The RAM address must start at 00000H, and the EPROM address must end at FFFFFH.

(10 Marks)

- b. Draw the internal architecture of 8255 PIO and explain in brief.

(06 Marks)

c. Explain Mode-1 and BSR modes of 8255.

(04 Marks)

#### Module-5

- 9 a. Interface ADC 0808 with 8086 CPU using 8255 ports. Use port A for transferring digital data of ADC to CPU, and port C for control signals. Assume that analog input is present at input-3 of ADC. Draw the schematic and write the required ALP. (10 Marks)

- b. Interface DAC0800 with 8086 CPU using port B of 8255. Write an ALP to generate a triangular waveform of frequency 400Hz. Assume that the system operates at 8MHz and the amplitude of the wave is 5V.

#### OR

- 10 a. Write an ALP to read a 2-digit hexadecimal number from keyboard, and display its 4-digit square value on the computer screen, using appropriate DOS function calls. Use assembler directives and comments in your program. (12 Marks)

- b. Write short notes on Von-Neumann architecture and Harvard architecture of computers with neat block diagrams. (08 Marks)

\* \* \* \* \*

## CBCS SCHEME

| USN 15E |

|---------|

|---------|

### Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 **Linear Integrated Circuits**

Time: 3 hrs.

Max. Marks: 80

Note: 1. Answer any FIVE full questions, choosing ONE full question from each module. 2. State the assumptions made.

Module-1

- Define the following parameters with respect to op-amp 1

- i) Input offset current

- Input offset voltage ii)

- iii) **CMRR**

- **PSRR** iv)

(08 Marks)

Sketch an illustration to show the effect of op-amp slew rate and explain. (04 Marks)

If a Non-inverting amplifier is designed for a gain of 50, using op-amp with 90dB CMRR, calculate common mode output (Vocm) for a common mode input (Vicm) of 100mV.

(04 Marks)

#### OR

- Design a direct-coupled non-inverting amplifier and explain its design steps. 2 (08 Marks)

- Two signals each ranging from 0.1V to 1V are to be summed. Using 741 op-amp design a suitable inverting summing circuit. (04 Marks)

- Design a inverting amplifier using 741 op-amp with voltage gain of 50. The output voltage amplitude is 2.5V (04 Marks)

#### Module-2

Draw the circuit to set the upper cut-off frequency using inverting amplifier and explain. 3 a.

A capacitor coupled non-inverting op-amp is to have gain of  $A_v = 66$  and  $V_i = 15$ mV with  $R_L = 2.2 \text{K}\Omega$  and  $f_1 = 120 \text{Hz}$ . Design the circuit. (08 Marks)

Explain with a neat circuit design, precision full wave rectifier and also its design steps.

Design a precision voltage source, with  $V_0 = 9V$  and supply voltage is  $\pm 12V$ . Allow 10% tolerance in zener diode [Assume 1N749 with  $V_z = 4.3V$ ]. (08 Marks)

#### Module-3

- Design a precision clipper to clip both ends, using dead zone circuit with relevant 5 waveforms, explain the same. (08 Marks)

- b. Design capacitor coupled zero-crossing detector with  $f_1 = 1$ kHz square wave input and  $V_{o(p-p)} = 6V$ . Use 741 op-amp with  $\pm 12V$  supply [Assume  $\Delta V = 1V$ ,  $V_B = 0.1V$ ]

OR

- 6 a. Define Barhausen's criteria. Explain with design, phase shift oscillator and with relevant waveforms. (08 Marks)

- b. Show the realization of logarithmic amplifier using an op-amp. Obtain the expression for the output voltage. (08 Marks)

#### Module-4

- 7 a. Write a brief note on the following op-amp applications:

- i) First order low pass filter

- ii) Second order high pass filter.

(08 Marks)

(06 Marks)

b. Design a single stage bandpass filter with frequency of  $f_1 = 300$ Hz and  $f_2 = 30$ kHz. Also state whether the design is narrow band or wide band. Use 741 op-amp for designing. [Assume  $c_2 = 1000$ pF]. (08 Marks)

#### OR

- 8 a. Explain the working of a series regulator using op-amp.

- b. With a neat internal diagram of IC723. Explain the functions of each block. Mention the advantages. (10 Marks)

#### Module-5

9 a. Explain D to A converter using R-2R network.

(08 Marks)

b. With a neat block diagram, explain the blocks of PLL.

#### (08 Marks)

#### OR

- 10 a. Explain 555 timer as Monostable muiltivibrator with waveforms.

- (08 Marks)

- b. Explain the working of A to D converter using successive approximation method. (08 Marks)

\* \* \* \* \*

# Third Semester B.E. Degree Examination, Jan./Feb.2021 Analog Electronics

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- a. With necessary equivalent diagram obtain the expression for Z<sub>in</sub>, A<sub>V</sub>, Z<sub>0</sub> for Darlington Emitter follower.

- b. For an Emitter bias circuit (capacitor bypassed), determine  $r_e$ ,  $Z_i$ ,  $Z_O$  and  $A_V$ . Given  $R_B=470~K\Omega$ ,  $R_C=2.2~K\Omega$ ,  $V_{CC}=20~V$ ,  $R_E=0.56~K\Omega$ ,  $C_E=10~\mu F$ ,  $\beta=120$ ,  $r_0=40~K\Omega$ ,  $C_C=10~\mu F$ .

OR

- a. Derive the expression for A<sub>V</sub>, A<sub>i</sub>, Z<sub>i</sub> and Z<sub>0</sub> for C<sub>E</sub> fixed bias configuration using complete hybrid equivalent model. (10 Marks)

- b. Consider a single stage CE amplifier with  $R_S = 1$  K and  $R_L = 1.2$  K $\Omega$ . Calculate  $A_i$ ,  $R_i$ ,  $A_V$ ,  $A_{is}$ , if  $h_{ie} = 1.1$  K,  $h_{re} = 2.5 \times 10^{-4}$ ,  $h_{fe} = 50$  and  $h_{oe} = 25 \,\mu\text{A/V}$ . (06 Marks)

Module-2

- 3 a. Derive the expression for transconductance g<sub>m</sub> for FET. (06 Marks)

- b. For the circuit shown in the Fig. Q3 (b), calculate (a)  $V_{GS}$  (b)  $I_{DQ}$  (c)  $V_{DSQ}$  (d)  $V_{D}$ .

(10 Marks)

Fig. Q3 (b)

- 4 a. With necessary equivalent circuit obtain the expression for A<sub>V</sub>, Z<sub>in</sub>, Z<sub>O</sub> for a fixed biased JFET amplifier. (08 Marks)

- b. Derive the expression for Z<sub>i</sub>, Z<sub>0</sub>, A<sub>V</sub> considering common drain amplifier circuit. (08 Marks)

Module-3

- 5 a. Derive the expression for lower cut-of frequencies due to various RC networks in CE amplifiers. (10 Marks)

- b. Determine the lower cut-off frequency for the emitter follower using BJT amplifier with  $C_S=0.1~\mu F$ ,  $R_S=1~K\Omega$ ,  $R_1=12~K\Omega$ ,  $R_2=4~K\Omega$ ,  $R_E=1.5~K\Omega$ ,  $C_C=0.1~\mu F$ ,  $\beta=100$ ,  $r_0=\infty$ ,  $V_{CC}=15~V$ ,  $V_{BE}=0.7~V$ .

#### OR

6 a. Describe Miller effect and derive an equation for Miller input and output capacitance.

(08 Marks)

b. Calculate the overall lower 3 dB and upper 3 dB frequencies for a 3 stage amplifier having an individual  $f_1 = 40$  Hz and  $f_2 = 2$  MHz. (08 Marks)

#### Module-4

- 7 a. Derive the expression for input resistance for a voltage of series and current series feedback.

(08 Marks)

- b. With a neat circuit diagram, explain FET based phase shift oscillator.

(08 Marks)

#### OR

- 8 a. With the help of neat circuit diagram. Explain the operation of Colpitts and Hartley oscillator. Write the expression for the frequency of oscillation. (12 Marks)

- b. In a transistor Colpitts oscillator  $C_1 = 1$  nF,  $C_2 = 100$  nF. Find the value of L for a frequency of 100 kHz. (04 Marks)

#### Module-5

- 9 a. Show that the transformer coupled class A power amplifier has maximum efficiency of 50%.

(08 Marks)

- b. A single transistor amplifier with transformer coupled load produces harmonic amplitudes in the output as.

$B_0 = 1.5 \text{ mA}$ ,  $B_1 = 120 \text{ mA}$ ,  $B_2 = 10 \text{ mA}$ ,  $B_3 = 4 \text{ mA}$ ,  $B_4 = 2 \text{ mA}$ ,  $B_5 = 1 \text{ mA}$

- (i) Determine the percentage total harmonic distortion.

- (ii) Assume a second identical transistor is used along with a suitable transformer to provide push pull operation. Use the above harmonic amplitudes to determine the new total harmonic distortion. (08 Marks)

#### OR

- 10 a. Explain with the block diagram, the basic types of voltage regulation circuit. (08 Marks)

- b. Explain the operation of complementary symmetry class B amplifier. (08 Marks)

\*\*\*\*

# Third Semester B.E. Degree Examination, Jan./Feb.2021 Network Analysis

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- 1 a. Define the terms with an example,

- (i) Linear and non linear elements.

- (ii) Lumped and distributed elements.

- (iii) Unilateral and Bilateral elements.

- (iv) Active and Passive elements.

(08 Marks)

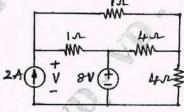

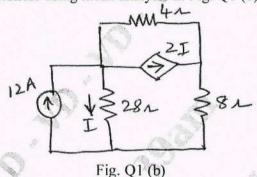

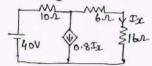

b. Find the current in 28  $\Omega$  resistor using mesh analysis in Fig. Q1 (b).

(08 Marks)

OR

2 a. Reduce the network in Fig. Q2 (a) to a single voltage source in series with a resistance using source shift and source transformation.

Fig. Q2 (a)

(08 Marks)

b. The node voltage equations of a network are,

$$\left[\frac{1}{5} + \frac{1}{j2} + \frac{1}{4}\right] V_1 - \frac{1}{4} V_2 = \frac{50 \angle 0^0}{5}$$

and

$$-\frac{1}{4}V_1 + \left[\frac{1}{4} + \frac{1}{-2j} + \frac{1}{2}\right]V_2 = \frac{50\angle 90^0}{2}.$$

Derive the network.

(08 Marks)

3 a. State and prove superposition theorem.

(08 Marks)

b. For the circuit shown in fig. Q3 (b), find the current through R<sub>L</sub> using Thevenins theorem. (08 Marks)

OR

4 a. State and prove Millers theorem.

(08 Marks)

b. Find the value of Z<sub>L</sub> for which power transferred to the load is maximum and also determine the maximum power for the circuit shown in Fig. Q4 (b). (08 Marks)

### Module-3

5 a. In the circuit of Fig. Q5 (a). Switch K is opened at t = 0. Find the value of V,  $\frac{dV}{dt}$  and  $\frac{d^2V}{dt^2}$  at  $t = 0^+$ .

Fig. Q5 (a)

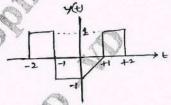

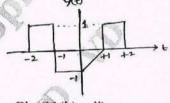

b. Obtain the Laplace transform of the square wave shown in Fig. Q5 (b).

(08 Marks)

6 a. State and prove initial value and final value theorem.

(08 Marks)

b. For the network shown in Fig. Q6 (b) the switch is moved from position 1 to position 2 at t = 0 the steady state has been reached before switching. Calculate i,  $\frac{di}{dt}$ ,  $\frac{d^2i}{dt^2}$  at  $t = 0^+$ .

(08 Marks)

### Module-4

- 7 a. Define the following terms:

- (i) Resonance

- (ii) Q-factor

- (iii) Bandwidth

- (iv) Selectivity.

(04 Marks)

- b. Derive an expression for frequency of resonance of a parallel resonant circuit containing resistance in both the branches. (06 Marks)

- c. It is required that a series RLC circuit should resonate at 500 kHz. Determine the values of R, L and C if the bandwidth of the circuit is 10 kHz and its impedence is 100 Ω at resonance. Also find the voltages across L and C at resonance if the applied voltage is 75 volts.

(06 Marks)

OR

- 8 a. Show that a two branch parallel resonant circuit is resonant at all the frequencies if  $R_L = R_C = \sqrt{\frac{L}{C}}$  where  $R_L =$  Resistance in the inductor branch,  $R_C =$  Resistance in the capacitor branch. (06 Marks)

- b. Give the comparison between series and parallel resonance.

(06 Marks) (04 Marks)

c. Find the value of R<sub>1</sub> such that the circuit given in Fig. Q8 (c) is resonant.

(06 Marks)

9 a. Express Y parameters in terms of Z and T parameters.

(08 Marks)

b. Find the transmission parameters for the network shown in Fig. Q9 (b).

(08 Marks)

OR

10 a. Express ABCD parameters in terms of Y and h parameters.

(08 Marks)

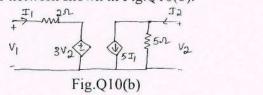

b. Find the h parameters of the network shown in Fig. Q10 (b).

(08 Marks)

Fig. Q10 (b)

15EC36

## Third Semester B.E. Degree Examination, Jan./Feb. 2021 Engineering Electromagnetics

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

a. A charge  $Q_A = -20 \mu C$  is located at A(-6, 4, 7) and a charge  $Q_B = 50 \mu C$  is located at B(5, 8, -2) in free space. If distances are given in meters, find the vector force exerted on  $Q_A$  by  $Q_B$ .

b. A charge of  $-0.3~\mu\text{C}$  is located at A(25, -30, 15) (in cm) and a second charge of 0.5  $\mu\text{C}$  is located at B(-10, 8, 12) cm. Find Electric field intensity (E) at

(i) the origin (ii) P(15, 20, 50, )cm.

(08 Marks)

c. Define electric flux density.

(02 Marks)

OR

2 a. Calculate the total charge within the universe of  $\rho_v = \frac{e^{-2r}}{r^2}$ . (04 Marks)

b. Infinite uniform line charges of 5 nC/m lie along the (positive and negative) x and y axes in free space. Find Electric field intensity (E) at P<sub>A</sub>(0, 0, 4) (04 Marks)

c. Calculate Electric flux Density (D) in rectangular coordinates at point P(2, -3, 6) produced by

(i) a point charge QA = 55 mC at Q(-2, 3, -6);

(ii) a uniform line charge  $\rho_{LB} = 20$  mC/m on the x-axis.

(08 Marks)

Module-2

3 a. State and explain Gauss law in electrostatics.

(04 Marks)

b. Derive the expression for electric field intensity due to an infinite line charge using Gauss law. (04 Marks)

c. In the region of free space that includes the volume 2 < x, y, z < 3,  $D = \frac{2}{z^2} (yza_x + xza_y - 2xya_z) c/m^2.$

(i) Evaluate the volume integral side of the divergence theorem for the volume defines here.

(ii) Evaluate surface integral side for the corresponding closed surface.

(08 Marks)

OR

4 a. Derive an expression for continuity equation in point form.

(04 Marks)

b. If Ê = 120 a<sub>p</sub> V/m, find the incremental amount of work done in moving a 50 μC charge a distance of 2 mm from (i) P(1, 2, 3) toward Q(2, 1, 4) (ii) Q(2, 1, 4) toward P(1, 2, 3).

(05 Marks)

c. Current density is given in cylindrical coordinates as  $J=-10^6$  z<sup>1.5</sup>a<sup>z</sup> A/m<sup>2</sup> in the region  $0 \le \rho \le 20$  µm; for  $\rho \ge 20$  µm J=0.

(i) Find the total current crossing the surface z = 0.1 m in the  $a_z$  direction.

(ii) If the charge velocity is  $2 \times 10^6$  m/s at z = 0.1m, find  $\rho_v$  (volume charge density).

(07 Marks)

5 a. Starting from Gauss law, derive Poisson's and Laplace's equation.

(04 Marks

b. Calculate numerical value for potential V and volume charge density  $\rho_{v}$  at  $P\left(3, \frac{\pi}{3}, 2\right)$  if  $V = 5\rho^{2} \cos 2\phi$ . (06 Marks)

c. Given the spherically symmetric potential field in free space,  $V = V_0 e^{-r/a}$ , find:

(i)  $\rho_v$  at r = a (ii) the electric field at r = a (iii) total charge.

(06 Marks)

#### OR

6 a. State and explain Ampere's law.

(04 Marks)

- b. Evaluate both sides of Stoke's theorem for the field  $H = 10 \sin \theta \, a_{\phi}$  and the surface r = 3,  $0 \le \theta \le 90^{\circ}$ ,  $0 \le \phi \le 90^{\circ}$ . Let the surface have the  $a_r$  direction. (06 Marks)

- c. Using the concept of vector magnetic potential, find the magnetic flux density at a point due to long straight filamentary conductor carrying current 'I' in the az direction. (06 Marks)

#### Module-4

- 7 a. Derive an expression for the force on a differential current element placed in a magnetic field. (04 Marks)

- b. A point charge for which  $Q = 2 \times 10^{-16}$  C and  $m = 5 \times 10^{-26}$  kg is moving in the combined fields  $E = 100 a_x 200 a_y + 300 a_z$  V/m and  $B = -3a_x + 2a_y a_z$  mT. If the charge velocity at t = 0 is V(0).  $V(0) = (2a_x 3a_y 4a_z)10^5$  m/s.

- (i) Give the unit vector showing the direction in which the charge is accelerating at t = 0.

- (ii) Find the kinetic energy of the charge at t = 0.

- c. A rectangular loop of wire in free space joins points A(1, 0, 1) to B(3, 0, 1) to C(3, 0, 4) to D(1, 0, 4) to A. The wire carries a current of 6 mA, flowing in the az direction from B to C. A filamentary current of 15A flows along entire z axis in the az direction.

- (i) Find 'F' on side BC' (ii) Find 'F' on side AB (iii) Find F<sub>total</sub> on the loop. (06 Marks)

#### OR

- 8 a. Given a material for which  $x_m = 3.1$  and within which  $B = 0.4ya_zT$ , find:

- (i) H (ii)  $\mu$  (iii)  $\mu_r$  (iv) M (v) J

(04 Marks)

- b. Let  $\mu_{r_1} = 2$  in region 1 defined by 2x + 3y 4z > 1 while  $\mu_{r_2} = 5$  in region 2 where 2x + 3y 4z < 1. In region 1,  $H_1 = 50a_x 30a_y + 20a_z A/m$ . Find:

- (i)  $H_{N_1}$  (ii)  $H_{t_1}$  (iii)  $H_{t_2}$  (iv)  $H_{N_2}$  (v)  $\theta_1$  the angle between  $H_1$  and  $a_{N21}$  (08 Marks)

- c. Obtain an expression for the total energy stored in a steady magnetic filed in which 'B' is linearly related to 'H'. (04 Marks)

#### Module-5

9 a. Write Maxwell's equations in integral and point forms.

(06 Marks)

- b. Using Faraday's law, deduce Maxwell's equation, to relate time varying electric and magnetic fields. (06 Marks)

- c. Explain the displacement current and displacement current density.

(04 Marks)

#### OR

10 a. Derive wave equations for uniform plane wave in free space.

(06 Marks)

- b. Derive an expression for propagation constant intrinsic impedance and phase velocity for a uniform plane wave propagating in a conducting media. (06 Marks)

- c. In free space  $E(x,t) = 50\cos(\omega t \beta x)a_y$  V/m. find the average power crossing a circular area of radius 5m in the plane x = constant. (04 Marks)

\*\* 2 of 2 \*\*

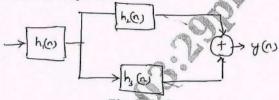

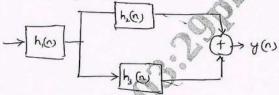

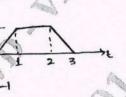

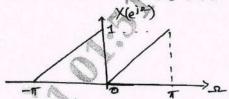

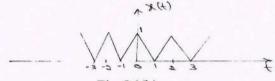

The LTI systems are connected as shown in Fig.Q.5(a). If  $h_1(n) = u(n-2)$ ,  $h_2(n) = nu(n)$  and 5  $h_3(n) = \delta(n-2)$ . Find the overall response. (10 Marks)

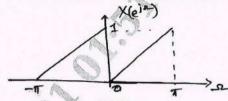

Evaluate the DTFS representation for the signal

$$x(n) = \sin\left(\frac{4\pi}{21}n\right) + \cos\left(\frac{10\pi}{21}n\right) + 1$$

Sketch the magnitude and phase spectra.

(10 Marks)

OR

- 6 State and explain following continuous time Fourier series properties:

- i) Time shift ii) Convolution iii) Parseval's Theorem.

(06 Marks)

(09 Marks)

- Check whether the system whose impulse response is b.

- i)  $h(n) = (1/2)^n u(n)$  ii)  $h(t) = e^{2t} u(t-1)$  stable, causal and memory less.

- Evaluate the step response for the LTI system represented by the following impulse response.  $h(t) = t^2 u(t)$ . (05 Marks)

Module-4

- State the following properties of DTFT: i) Linearity ii) Frequency shift 7 iii) Frequency differentiation iv) Modulation v) Convolution. Obtain the FT of the signal  $x(t) = e^{-at} u(t)$ ; a > 0. (10 Marks) (10 Marks)

- OR Find DTFT of the signal  $x(n) = \{1, 3, 5, 3, 1\}$  and evaluate  $X(e^{j\Omega})$  at  $\Omega = 0$ 8

- (06 Marks) (08 Marks)

- With neat diagrams, state and explain sampling theorem. b.

- Determine the Nyquist sampling rate and Nyquist sampling interval for

- $x_1(t) = \cos(5\pi t) + 0.5\cos(10\pi t)$  ii)  $x_2(t) = \operatorname{Sinc}^2(200t)$

(06 Marks)

- Define Z-transform. Mention the properties of Region of Convergence (ROC). 9 (06 Marks)

- Determine the Z transform of these signals

i)

$$x_1(n) = n\left(\frac{5}{8}\right)^n u(n)$$

ii)  $x_2(n) = (0.9)^n u(n) * (0.6)^n u(n)$  (08 Marks)

Find Inverse Z transform, if  $X(z) = \frac{\left(\frac{1}{4}\right)z^{-1}}{\left(1 - \frac{1}{2}z^{-1}\right)\left(1 - \frac{1}{4}z^{-1}\right)}$  for all possible ROCs. (06 Marks)

- Prove the following properties of Z-transform: i) Linearity ii) Time Reversal. 10

- A system has impulse response  $h(n) = (\frac{1}{2})^n u(n)$ . Determine the input to the system if the

output is given by

$$y(n) = \frac{1}{3}u(n) + \frac{2}{3}(-\frac{1}{2})^n u(n)$$

. (12 Marks)

### Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 Signals and Systems

Time: 3 hrs. Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

#### Module-1

- a. Define a signal. List the elementary signals. Differentiate between even and odd signals, energy and power signals. (08 Marks)

- b. Sketch the signal x(t) = r(t+1) r(t) + r(t-1). (04 Marks)

- c. Check whether the following signals are periodic or not. If periodic, determine the fundamental period:

i)

$$x(n) = \cos\left(\frac{\pi n}{2}\right) + \sin\left(\frac{\pi n}{4}\right)$$

ii)

$$x(t) = \cos(2\pi t) \sin 4\pi t$$

(08 Marks)

#### OR

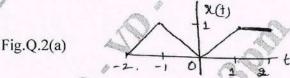

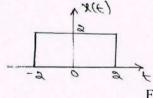

2 a. Determine and sketch the even and odd components of the signal x(t) shown in Fig.Q.2(a).

(08 Marks)

Fig.Q.2(a)

- Fig.Q.2(a

- b. Find and sketch the derivatives of the following signals: x(t) = u(t) u(t a), a > 0.

- c. Check whether the following system is

- i) Static or dynamic

- ii) Linear or nonlinear

- iii) Time invariant or time variant

- iv) Causal or non causal

- v) Stable or unstable

- vi) Invertible or non invertible. y(n) = log[x(n)]

(08 Marks)

### Module-2

3 a. Derive the expression for convolution integral.

(07 Marks)

- b. Prove the following: i)  $x(n) * \delta(n) = x(n)$  ii)  $x(n) * u(n) = \sum_{k=-\infty}^{n} x(k)$  (06 Marks)

- c. Consider a LTI system with unit impulse response  $h(t) = e^{-t}u(t)$ . If the input applied to this system is  $x(t) = e^{-3t}(u(t) u(t-2))$ . Find the output y(t) of the system. (07 Marks)

#### OR

- 4 a. State and prove commutative and distributive properties of convolution integral. (08 Marks)

- b. The impulse response of LTI system is  $h(n) = \{1, 2\}$ . Determine the response of the system to input signal  $x(n) = \{1, 3, 1\}$  using graphical method. (06 Marks)

- c. Find the discrete time convolution sum given below:

$$y(n) = \beta^{n}u(n) *\alpha^{n}u(n), |B| < 1, |\alpha| < 1$$

(06 Marks)

### Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 Control Systems

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- a. Differentiate between Open loop control system and Closed loop control system. (06 Marks)

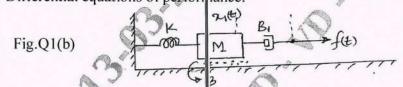

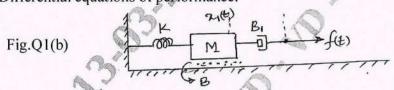

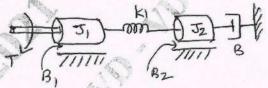

- b. For the mechanical system, shown in fig. Q1(b), write the i) Mechanical network;

ii) Differential equations of performance. (06 Marks)

c. Obtain the transfer function of the system shown in fig. Q1(c).

(08 Marks)

OF

- 2 a. Explain the block diagram rule regarding: 1) Combining blocks in cascade

- ii) Moving a take off point beyond a block.

(04 Marks)

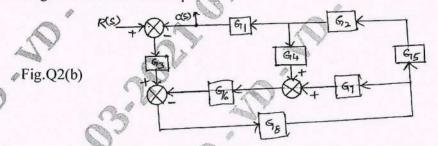

Determine the transfer function C()/R(s) for the block diagram shown in fig. Q2(b), using

- block diagram reduction techniques

(08 Marks)

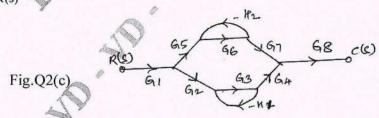

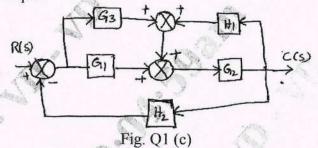

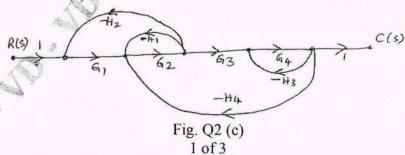

c. Find  $\frac{C(s)}{R(s)}$  for the following signal flow graph of fig. Q2(c).

(08 Marks)

- a. With usual notation, derive an expression for the Peak time (t<sub>p</sub>) and Rise time (t<sub>r</sub>) of a response of second order system to a unit step input.

(06 Marks)

- b. Explain PI and PID controllers of a control system.

(06 Marks)

c. A second order control system is represented by a transfer function given below:

$\frac{Q(s)}{T(s)} = \frac{1}{Js^2 + Bs + K}, \text{ where } Q(s) \text{ is the proportional output and } T(s) \text{ is the input torque.}$

A step unit of 10N-mt is applied to the system and test results are given below:

i) Maximum overshoot is 6% ii) Peak time is 1 sec iii) Steady static value of the output is 0.5 radian. Determine the values of J, F and K. (08 Marks)

#### OR

- 4 a. Define Steady state error and Static error coefficients with respect to step input, velocity input and acceleration inputs. (06 Marks)

- b. For a unity feedback system  $G(s) = \frac{s(s+1)}{s^2(s+3)(s+10)}$ . Determine the type of system, error coefficients and steady state error for input  $\gamma(t) = 1 + 3t$ . (06 Marks)

- c. A signal is represented by the equation  $\frac{d^2\theta}{dt^2} + 10.\frac{d\theta}{dt} = 150.e$ . Where  $e = (r-\theta)$  is the actuating signal. Calculate the value of damping ratio, undamped and damped frequency of oscillation. Also determine Open loop transfer function. (08 Marks)

#### Module-3

5 a. State R – H criterion and discuss its limitation.

(06 Marks)

b. State the different rules for the construction Root locus.

(06 Marks)

c. The open loop transfer function of a unity feedback system is given by

$G(s) = \frac{K}{s(s+3)(s^2+s+1)}$ . Determine the value of K that will cause sustained oscillations in

the closed loop system. Also find the frequency of sustained oscillations.

(08 Marks)

#### OR

6 a A unity feedback control system has G(s) =

Cleatale the weet leave and aleas

OR

8 a. Explain Lag – lead compensating networks.

(06 Marks)

- b. Given  $G(s)H(s) = \frac{12}{s[s+1][s+2]}$ . Draw the Polar plot and hence determine if system is stable? (06 Marks)

- c. The open loop transfer function of a control system is  $G(s)H(s) = \frac{1}{s^2(s+2)}$ . Sketch the Nyquist plot, Path and asertain the stability. (08 Marks)

Module-5

- 9 a. What is Signal Reconstruction? Explain it with SAMPLE and HOLD circuit. (06 Marks)

- b. Find the State transition Matrix for  $A = \begin{bmatrix} 0 & -1 \\ +2 & -3 \end{bmatrix}$ . (06 Marks)

- c. Consider the system given by  $\ddot{y} + 9\ddot{y} + 26\dot{y} + 24y = 6$  U. Obtain its state model. (08 Marks)

OR

10 a. List the properties of State transition matrix

(06 Marks)

b. Explain Spectrum analysis of Sampling process.

(06 Marks)

c. Obtain the transition matrix Q(t) of the following system

$\begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} = \begin{bmatrix} 0 & 1 \\ -2 & -3 \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix}.$  Also obtain the inverse of the transition matrix  $\phi^i(t)$ . (08 Marks)

17EC44

# Fourth Semester B.E. Degree Examination, Jan./Feb. 2021 Principles of Communication Systems

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

#### Module-1

- 1 a. Illustrate the amplitude modulation process. What is envelope distortion? (10 Marks)

- b. With the aid of neat block diagram, describe coherent detection of DSB-SC modulated wave. What is quadrature null effect? (07 Marks)

- c. A single of 5KHz frequency signal is modulated on a carrier wave of a frequency 2 MHz. What are the frequencies of the resultant signal? (03 Marks)

#### OR

- 2 a. Describe ring modulator. Why the ring modulator is referred as a double balanced modulator?

(10 Marks)

- b. Describe quadrature carrier multiplexing. (06 Marks)

- c. What are the factors influencing the choice of VSB modulation for the transmission of analog TV signals? (04 Marks)

#### Module-2

3 a. Derive an expression for FM signal.

(08 Marks)

b. With the aid of neat block diagram, explain AM super heterodyne receiver.

(08 Marks)

c. The resulting FM signal is  $10 \text{ Cos}[(2\pi 10^5 \text{t}) + 15 \text{ Sin } (2\pi 100 \text{t})]$ . Find the approximate bandwidth of the FM signal. (04 Marks)

#### OR

4 a. Describe the PLL working.

(08 Marks)

b. With the aid of neat circuit diagram balanced frequency discriminator.

(08 Marks)

c. What are the RF frequency range and intermediate frequency for AM and FM ratio?

(04 Marks)

#### Module-3

- 5 a. Define Mean, correlation and covariance Functions of a random process x(t). (08 Marks)

- b. Discuss Gaussian process and its properties.c. Draw the characteristics of white noise.

(08 Marks) (04 Marks)

#### OR

6 a. Write the important properties of autocorrelation function.

(08 Marks)

b. Discuss shot noise, and thermal noise.

(08 Marks)

c. Define noise equivalent bandwidth.

(04 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

- Discuss noise in DSB-SC. Show that figure of merit for DSB-SC receiver is one. (10 Marks)

- Discuss pre-emphasis and de-emphasis in FM

(10 Marks)

Derive the expression for figure of merit for FM. 8

(14 Marks)

Show that figure of merit for single tone AM modulation is equal to 1/3 for 100% modulation. (06 Marks)

#### Module-5

With the aid of block diagram, describe PPM Generation and detection. 9 (10 Marks)

- Design a PCM multiplexing system using 256 levels signal quantizer for the transmission of 3 signals: m<sub>1</sub> m<sub>2</sub> and m<sub>3</sub> band limited to 5KHz, 10KHz and 5KHz respectively. Assuming that each signal is sampled at its Nyquist rate and 8 bits are transmitted simultaneously. Compute: \_<

- Maximum bit duration i)

- Channel Bandwidth required to pass PCM signal

- iii) The commutator speed in RPM.

(10 Marks)

#### OR

10 Describe the basic elements of a PCM system.

(10 Marks)

- State sampling theorem. Find the Nyquist sampling rate for the signa

- $g(t) = 10 \text{ Cos} (50\pi t) \text{ Cos}^2 (150\pi t)$  where t is in mscees.

(06 Marks)

c. Represent the binary data given below interms of i) unipolar NRZ signaling ii) Split phase. Binary data: 0110101. (04 Marks)

## GBGS SCHEME

| JSN |  |  |  |  |  |

|-----|--|--|--|--|--|

|     |  |  |  |  |  |

# Fourth Semester B.E. Degree Examination, Jan./Feb.2021 Microprocessors

Time: 3 hrs.

Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice.

Max. Marks: 80

| - 11 | 110.     | Widx. IV.                                                                                                                          | laiks. ou                |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|      | N        | ote: Answer any FIVE full questions, choosing ONE full question from each mo                                                       | odule.                   |

|      |          | Module-1                                                                                                                           |                          |

| 1    | a.<br>b. | Define Microprocessor. With a neat diagram, describe the architecture of 8086. Explain the significance of following pins of 8086: | (08 Marks)               |

|      |          | (i) ALE (ii) $MN/\overline{MX}$ (iii) $M/\overline{I/O}$ (iv) $DT/\overline{R}$ .                                                  | (04 Marks)               |

|      | c.       | Write an ALP to reverse a data block without using a dummy block.                                                                  | (04 Marks)               |

|      |          | OR                                                                                                                                 |                          |

| 2    | a.       | The Opcode for MOV instruction is "100010". Determine Machine Language of following instructions:                                  | code for the             |

|      |          | (i) MOV BL, CL (ii) MOV [S1], DL                                                                                                   | (04 Marks)               |

|      | b.       | Explain the following instructions, with examples:                                                                                 |                          |

|      | 0        | (i) XLAT (ii) LDS (iii) AAM                                                                                                        | (06 Marks)               |

|      | C.       | Write an ALP to add two, 16 bit (4 digit) BCD numbers. Ignore the end-around ca                                                    | arry.<br>(06 Marks)      |

| 3    | a        | Module-2 Write an ALP to convert a 16 bit binary number to BCD.                                                                    | (06 Montre)              |

| 3    | b.       | If $AX = 1234$ H, Trace the output in AX after the execution of following instructions                                             | (06 Marks)               |

|      | Ů.       | (i) SHL AX, 1 (ii) ROR AX, 1.                                                                                                      | (04 Marks)               |

|      | c.       | Explain any three string instructions of 8086.                                                                                     | (06 Marks)               |

|      |          | OR                                                                                                                                 |                          |

| 4    | a.       | Write an ALP to find number of 1's and 0's in a given 16 bit number.                                                               | (06 Marks)               |

|      | b.       | What are assembler directives? Explain the following assembler directives with a                                                   | n example:               |

|      |          | (i) DW (ii) OFFSET.                                                                                                                | (06 Marks)               |

|      | C.       | Explain any four Flag Manipulation Instructions of 8086.                                                                           | (04 Marks)               |

|      |          | Module-3                                                                                                                           |                          |

| 5    | a.       | Explain the stack structure of 8086.                                                                                               | (06 Marks)               |

|      | b.<br>c. | Explain the Interrupt cycle of 8086.  Write an ALP to find factorial of a 8 bit binary number.                                     | (04 Marks)<br>(06 Marks) |

|      |          | OR                                                                                                                                 |                          |

| 6    | a.       | Explain passing parameters to procedures with an example program.                                                                  | (06 Marks)               |

|      | b.       | Explain MACROS in 8086, with an example.                                                                                           | (04 Marks)               |

|      | C.       | Write a program to generate a delay of 10 minutes using 8086 microprocessor of 10 MHz frequency. Show delay calculation in detail. | perating on (06 Marks)   |

- Explain maximum mode of 8086 with a neat block diagram. Write the memory read timing diagram.

(10 Marks)

- b. Explain I/O addressing capability of 8086.

(06 Marks)

#### OR