KLS Vishwanathrao Deshpande Institute of Technology

ALBOS E

(Accredited by NAAC with "A" Grade)

(Approved by AICTE, New Delhi, Affiliated to VTU, Belagavi)

(Recognized Under Section 2(f) by UGC, New Delhi)

Udyog Vidya Nagar, Haliyal - 581 329, Dist.: Uttara Kannada

Phone: 08284 - 220861, 220334, 221409, Fax: 08284 - 220813

www.klsvdit.edu.in | principal@klsvdit.edu.in | hodece@klsvdit.edu.in

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## <u>University / Model Question Paper</u> <u>Scheme & Solution</u>

| Faculty Name           | : DEEPAK SHARMA |

|------------------------|-----------------|

| Course Name            | : VLSI DESIGN   |

| Course Code            | : 18EC72        |

| Year of Question Paper | : 2023 - 24     |

| Date of Submission     | 15/04/2024      |

Faculty Member

Head of the Department

Dean (Acad.)

## Seventh Semester B.E. Degree Examination, Dec.2023/Jan.2024 **VLSI** Design

Time: 3 hrs.

Max. Marks: 100

Note: 1. Answer any FIVE full questions, choosing ONE full question from each module. 2. Missing data may be suitably assumed.

Module-1

- 1 Derive an expression for drain current in linear and saturation region Draw the CMOS inverter circuit and explain its D.C. characteristic.

- Implement a 2:1 MUX using transmission gate.

(08 Marks) (04 Marks)

(08 Marks)

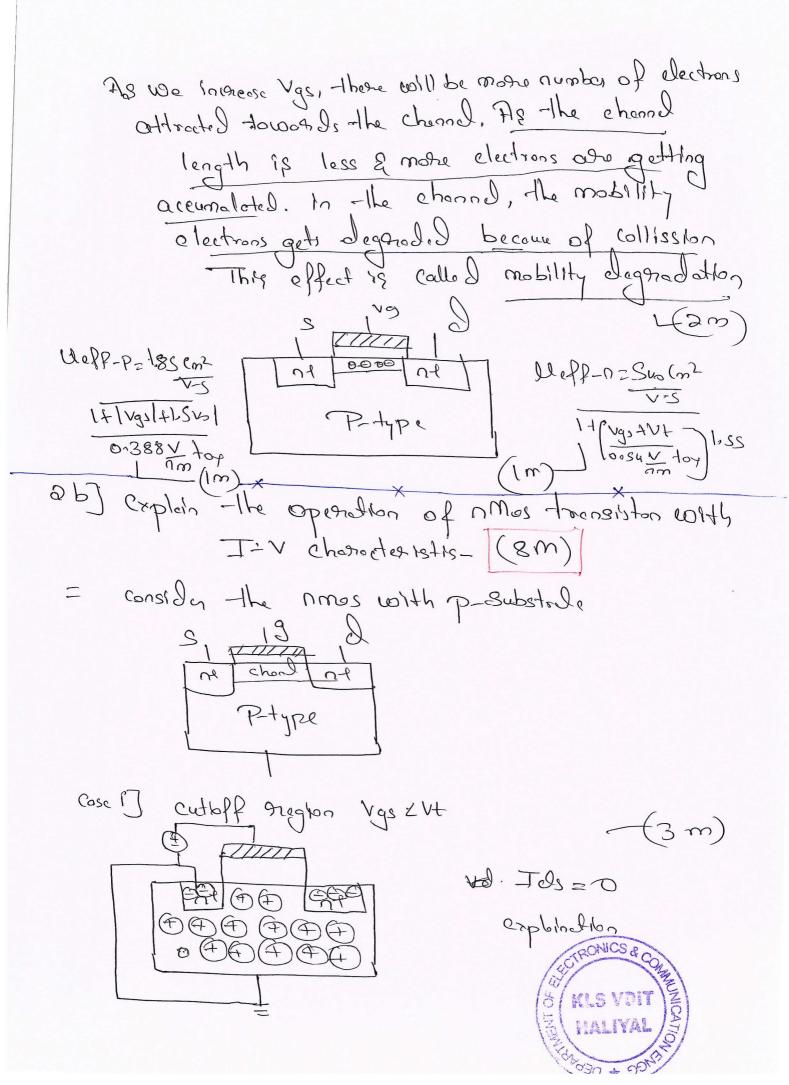

- Explain the non ideal IV effect of MOSFET with respect to CMOS channel length modulation and mobility degradation. (08 Marks)

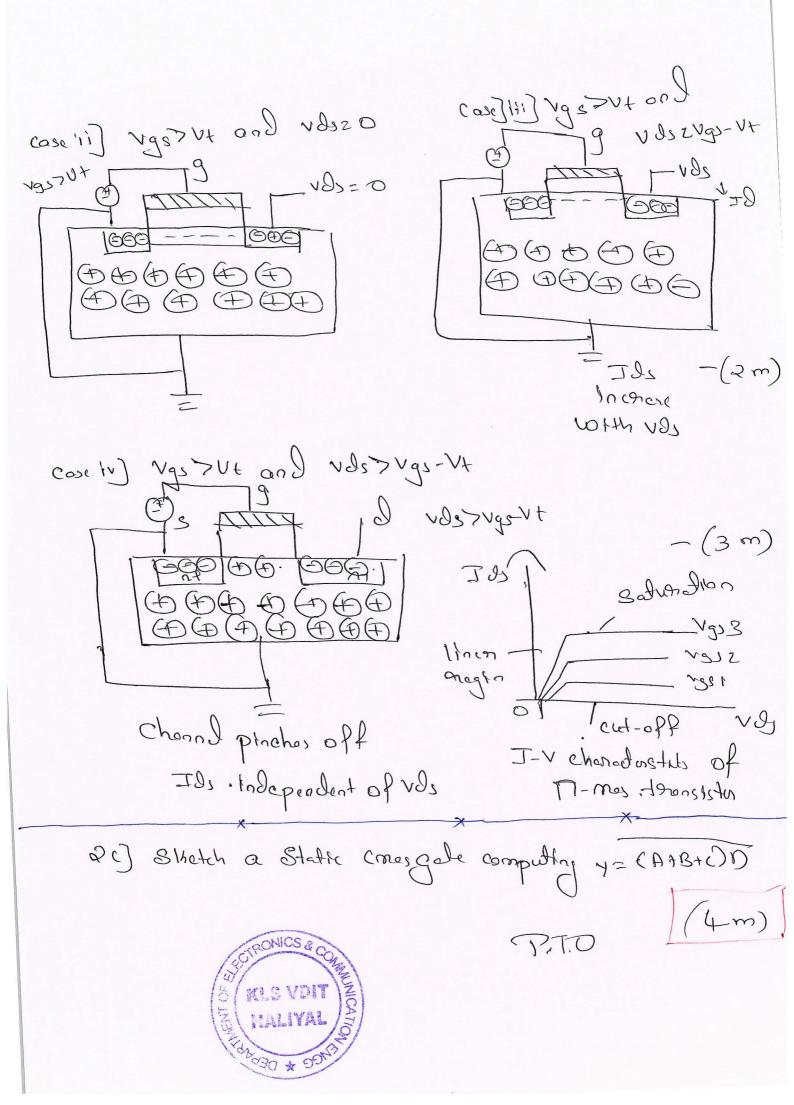

- Explain the operation of nMOS transistor with IV characteristics. b.

(08 Marks)

Sketch a static CMOS gate computing y = (A + B + C)D

(04 Marks)

Module-2

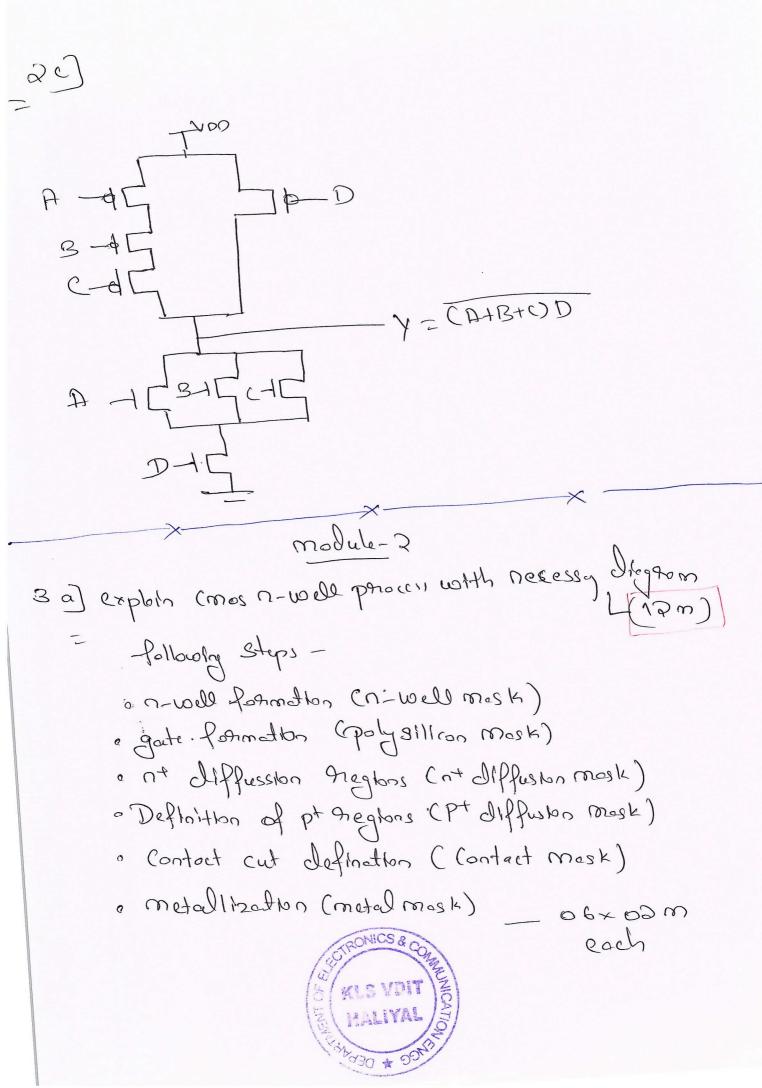

Explain CMOS nWell process with necessary diagrams.

(12 Marks)

Mention different types of MOSFET capacitances with necessary diagrams and equations also MOSFET. Capacitances in cut off, linear and saturation region. (08 Marks)

- Define scaling. Explain constant field scaling and constant voltage scaling and why constant voltage scaling is usually preferred over full scaling. (07 Marks)

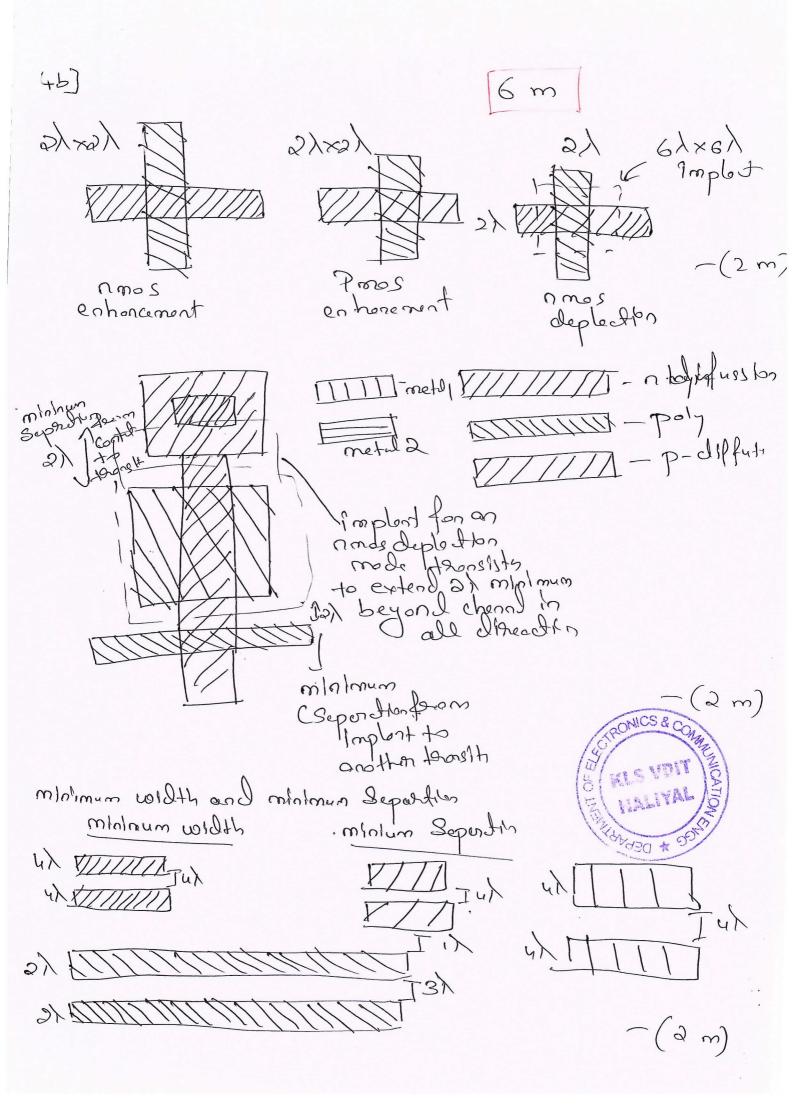

- With neat diagram, explain the Lambda based design rules for two metal layers.

(06 Marks)

Draw the layout for f = ABC and estimate the cell area.

(07 Marks)

Module-3

- Develop the RC delay model to compute the delay of the logic circuit and calculate the delay of unit sized inverter driving another unit in vertex. (06 Marks)

- b. Estimate tpdf and tpdf for the 3 input NAND gate shown in Fig.Q.5(b) if the output is loaded (08 Marks) with h identical NAND gates.

Fig.Q.5(b)

l of 2

Explain eVSE with an example.

(06 Marks)

NICS & C

Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

2. Any revealing of identification, appeal to evaluater and /or equations written eg. 42+8 = 50, will be treated as malpractice.

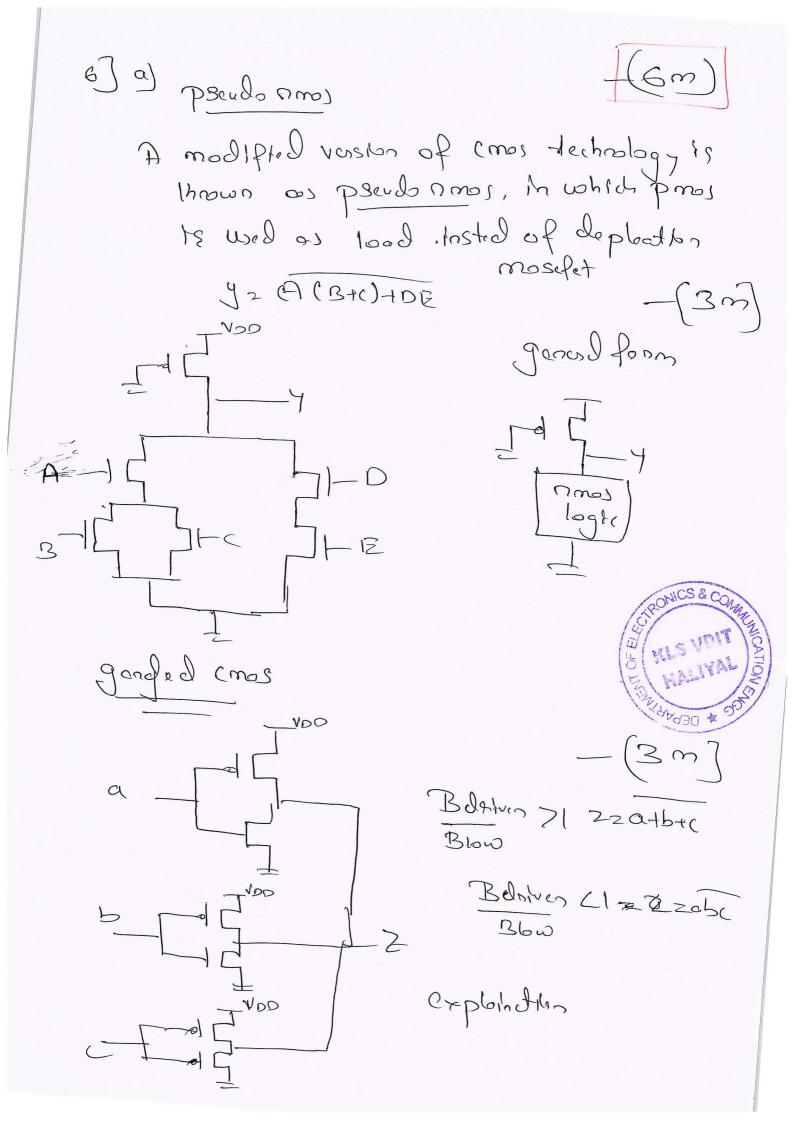

- Explain: i) Pseudo-nMOS

- OR

- ii) Ganged CMOS with necessary circuit examples.

- b. If a unit transistor has  $R = 10 \text{K}\Omega$  and  $e = 0.10^\circ$  in a 65nm process, compute the delay, in picoseconds, of the inverter Fig.Q.6(b) with a fan out of h = 4. (06 Marks)

Fig.Q.6(b)

- c. Explain linear delay model compare the logical effort of the following gates with the help of schematic diagrams: i) 3-input NAND gate ii) 3 input NOR gate.

- Module-4

- Explain Resettable latches and flipflops using CMOS transmission gate.

(06 Marks)

b. Explain Dynamic logic.

7

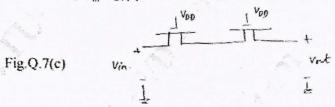

Consider the two nFET chain in Fig.Q.7(c). The power supply is set to a value of (06 Marks)  $V_{DD} = 3.3V$  and the nFET threshold voltage is  $V_{Tn} = 0.55V$ . Find the output voltage  $V_{out}$  at the right side of the chain for the following values: i)  $V_{sn} = 2.9V$  ii)  $V_{in} = 3.0V$ iii)  $V_{in} = 1.4V$  iv)  $V_m = 3.1V$

OR

Explain pulsed latches with schematic and waveforms.

(06 Marks)

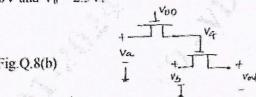

- The output of an nFET is used to drive the gate of another nFET as shown in Fig.Q.8(b). Assume that  $V_{DD} = 3.3V$  and  $V_{tn} = 0.6V$ . Find the output voltage  $V_{out}$  when the input voltages are at following values:

- $V_0 = 3.3V$  and  $V_b = 3.3V$ 1)

- $V_0 = 2.0V$  and  $V_0 = 2.5V$ .

(08 Marks)

Explain Domino logic.

(06 Marks)

## Module-5

With neat schematic diagram explain the operation of Full CMOS static RAM cell. 9

(10 Marks)

Explain the different fault models.

(10 Marks)

OR

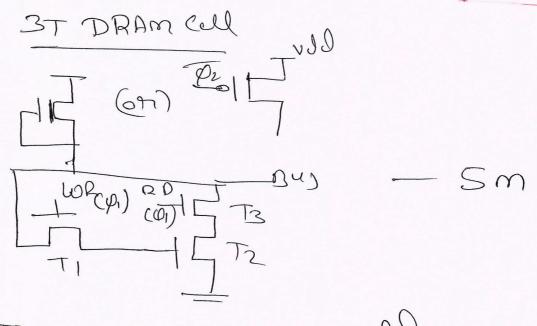

With neat schematic diagram explain the operation of three transistor DRAM cell.

(10 Marks)

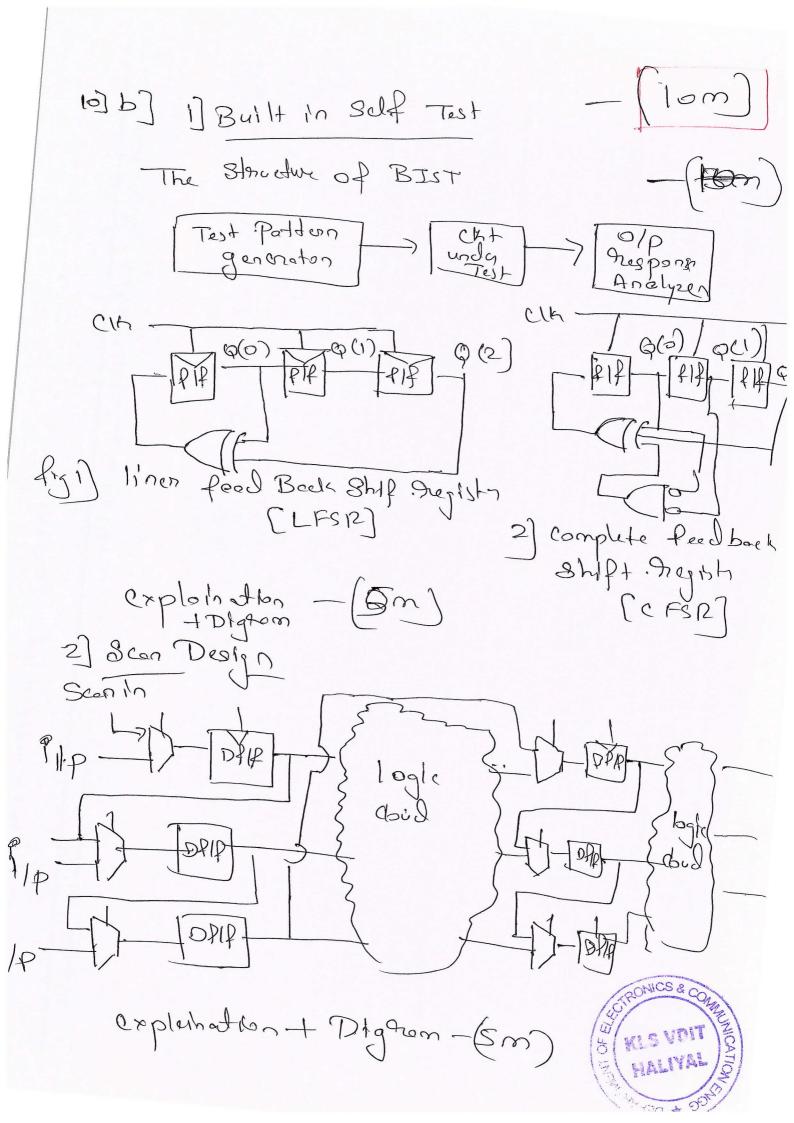

Write short notes on: i) Built in Self Test ii) Scan Design. (10 Marks)

\*\*\*\* 2 of 2

## module-1

1 a) Dessine an exponession for Isain Custrent in linear and Saturation neglion

Unear neglon non-Saturated

Saturation current

(2m)

16) Paraco-the (mos sovertion cht and explain 1ts De Charactersti - 8 m Comos Povortes Vgsn=Vln, Vgsp=-(vpo-Vln) - (Im) volsn=voul, volsp=(von-but) - (m) explaination - (3m) VTC-(3m) a D!Imux wing transmission gate - Lam

20) Exploin the non-Ideal IV effect of mosfet with nespect to mos chand length modualation and mobility alegandration. \_8m

= channel length modulation

Form the I-V charactorsticks, when Vds 15 greater than or equal to vgs-V+L, the mosfet becomes Baturaded, as Shown below

Josh regs Leff-L-Ld

-----vgs

Ids=BVs7(1+vd1)-(2m)

lee foor the given value of vgs, even if vos is increased beyond vgs-ve, the Isalin current (ID) sumaine Const & But in Aelity, If vos is inchessed buyond vgs-Vt,

The dacin current (ID) increase Blightly, - this phenomenon is called as "chand length modulation" (2m) (nepresentil by blotted line in graph)

mobility degradition w 19t

> V=JUE v- velocity le- mobility E- Electric PIDD.

mertion différent types of MosfET Carpacitana with necessary diagram and equations also mosfET Capaeltance in cutally lincon and Saturation Togd Togd Togd most ET 3

The Gate Fig. 13

The Diagram - (4m) exploration of oxide analated capacitans with Egb Egs & Egs, Egr equation exploration of junction especitare with

five junction Repaidance indication 4 a) Define Scaling, explain constat field Scaling and constat Solfage Sealing and why constit voltge Scaly

Solfage Is usual preferred then own full Sealy for toted act Definition of Scaling and digton (Dm) NO SUPERS KLSVOIT

y 2 DBC Euler groph Oay -(3m)22 VDD APABO \*

> Area = Height = (4+1) \*8 1 = 5 x8 1 = 40 1 width = 4 x8 1 = 327.

Tac Tac Tac Tac Tac Tac FRT ( - (1 m) 5 b] +plf = (3c)(\frac{P}{3}) + (3c)(\frac{P}{3} + \frac{P}{3}) + (9+5A)() (\frac{P}{5} + \frac{P}{3}) +pdp= (1s+sh) Re  $P_{13} = \frac{1}{1}(q+3h)($   $P_{13} = \frac{1}{1}(q+3h)($ CVSL coscolo Voltage Switch logic The difference of the second o ExploIndbn

1-tpd-1

-(1 m)

Rc product in 65 nm process is

RxC

-(1 m)

= lokxonlAF

= 1PS

Fan out is equil tazy

-i. deloy is (3+3h) RC - (2m)

= (3+3x4) x1ps

= 15ps - (2m)

exploration of threa older model with the equition . dzf+p - (2m) legico. Offont computation 3/p Nor ILP NAND Ch26 logic effort gz to logic effort 3/1pNOR=9=7.

module - 4 (6m 7 a Symbol nes I nesd definden g - Im Synchhonous Tresat definden A Synchhanous Fresch Synchron herelj A Synchronous neset! (lm)explaination L(Im) Treset Frest

(6 m) Dyromic logic implementen Offers Lower power Consumation Thon Static logic implementan (1m) example for Dymonic logic . Clat Dynamic. D. latch ext. D Tex -(on) explaination - (2m) 7c) Vout (max) = Vos - Vtn (8m)Case ] Vinza, 9 0 = 3,3 - 0,55 = 2,75 V (asi2) Vin=3, V= 3,3-0,55 = 0.75 v Case3) vincloy voz VIn = lokyv Case4) vin=311 Voz Voo-VTn= 2.75v

P70

8a] Pulsed latches 600 A pulsed · latch can be built from a · Convential comes transport latch · datum by a batef clk pulse \_\_\_\_ Im explainton (1m)

8.b)

No.23.3

No.23.

let us consider a dynamic comos logic gate which implement the function P= A1A2 F13+B1B2 Imp (phechoge mosflet) P= D, A2A3 + B, B2 me (Evalute MOSFET) explaination - (3m)

module-5

lom 9 a) SRAM menoty chts are designed to purmit Outobe 31 le de de Bits de be stared in cetare as well as gretolist on demont Depending on the present state of the two Yoventer latch . C14t, the date below held in the memory call will be integrated orther as logic oon? Ishally two not pass of roasiton out implements To connect the 1-bit SPAM cull to the Complementy likes popular 1-bit BRAmell a) Sylonoble Aephesentha 5) genere Obord full cross SRAM cell explandon of all three fill -

KLS VOIT HALIYAL ON # SOUTH

MALIYAL OF TOM 95) Fault models · In order to datenme good and bod pand, in a chip. It is necessary to propose a fault model. This model will help to know when and how fault occur, what is their trapaet on cht. The most popular model is called the Stuck-At modd. The Short Cht/open Cht. 13 another model can be a closer fit to Irelaity but this is difficult to implement Standi-At Foults - explonion (500) ) o If fourt 1200 | Sea-1 , 11 fourt Sza-0 1121 ---1221 S-a-0

او) م

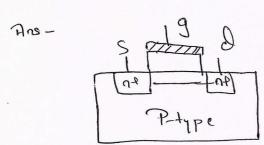

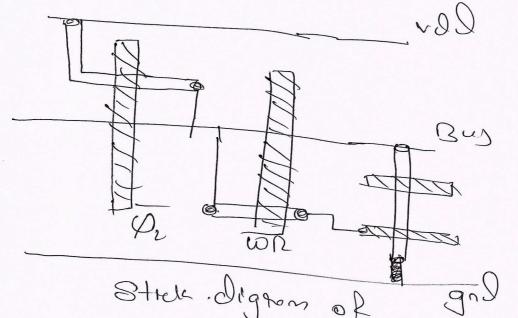

Stick dignom of 3T-DRAM

explorindon - (5m)